# LCD Monitor Service Manual

# MODEL: LCT-17HT

Model No.: LCT-17HT

# **CONTENTS**

| SPECIFICATION                             | 4   |

|-------------------------------------------|-----|

| PANEL: HT17E12-200                        | 5   |

| 8 BIT MTP MICROCONTROLLER                 | 27  |

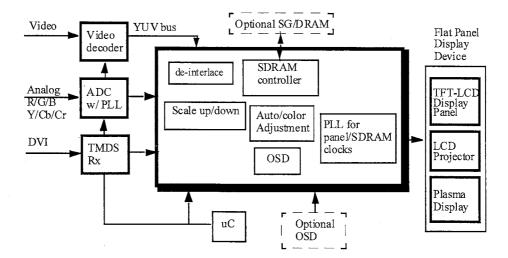

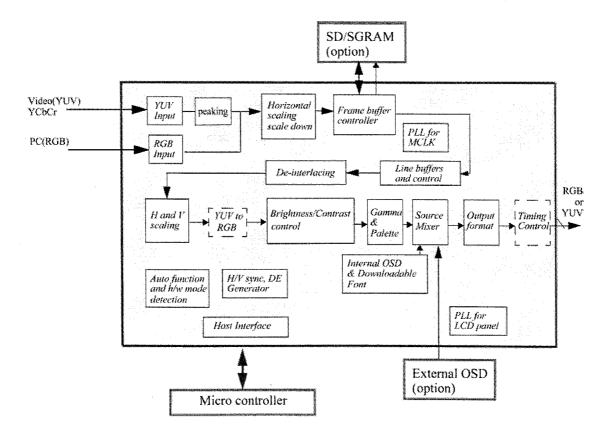

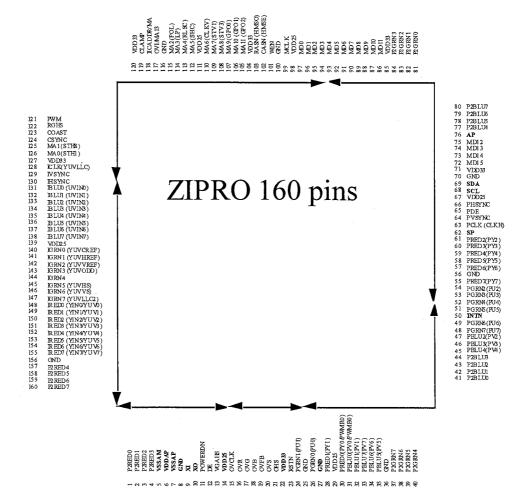

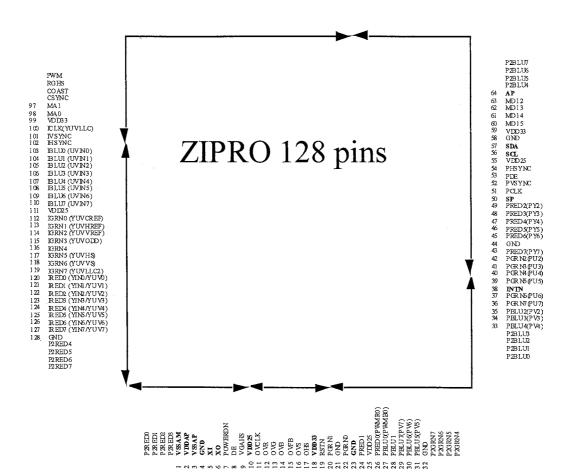

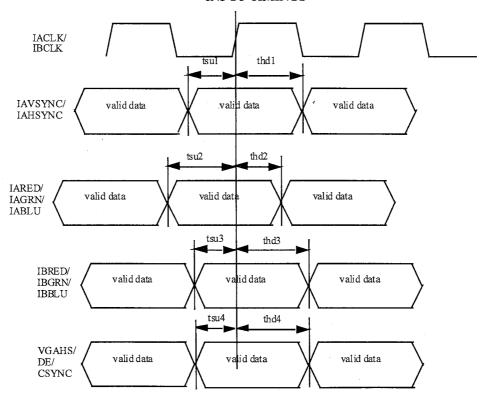

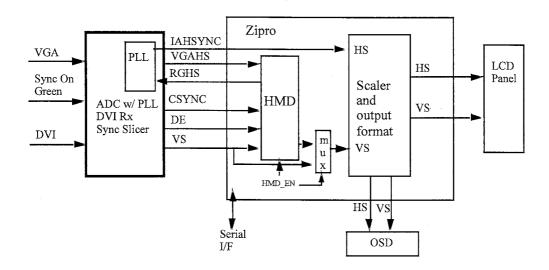

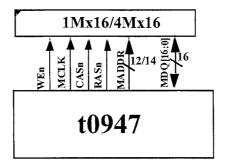

| T0947 SCALER IC FPR XGA/SXGA LCD MONITORS | 63  |

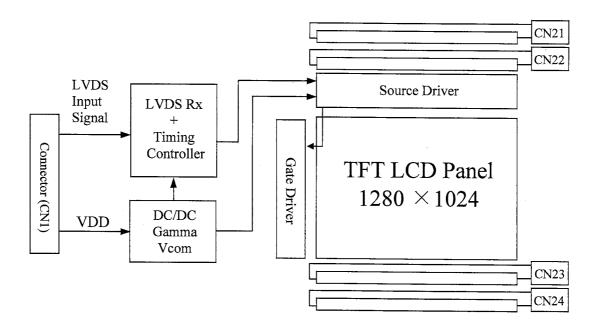

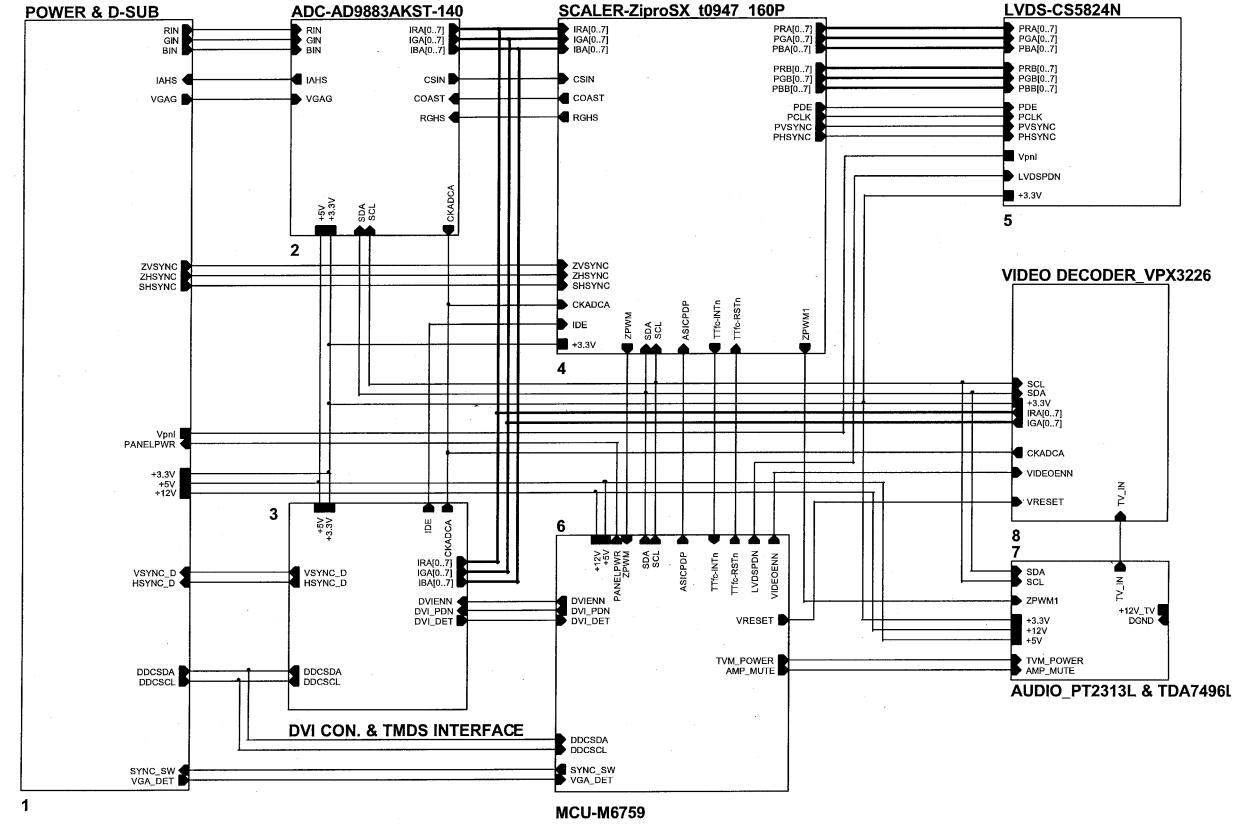

| BLOCK DIAGRAM                             | 184 |

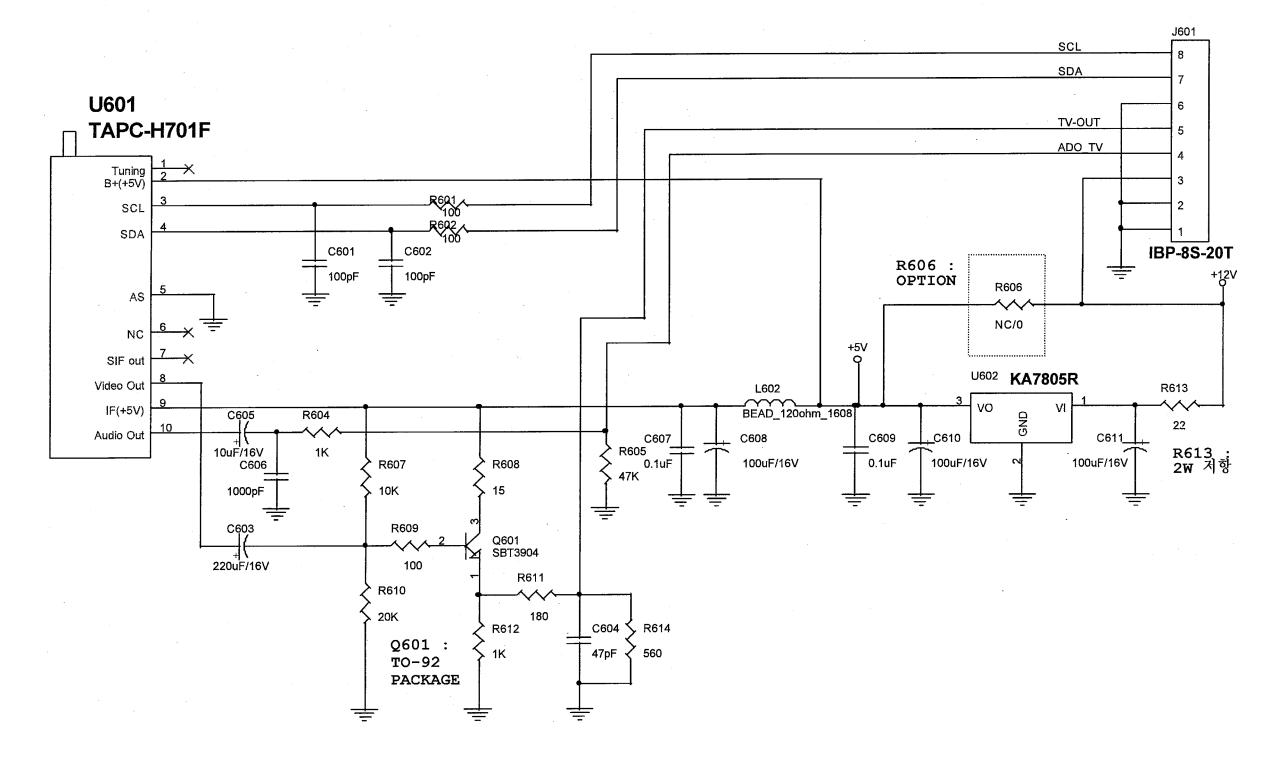

| TV TUNER                                  | 185 |

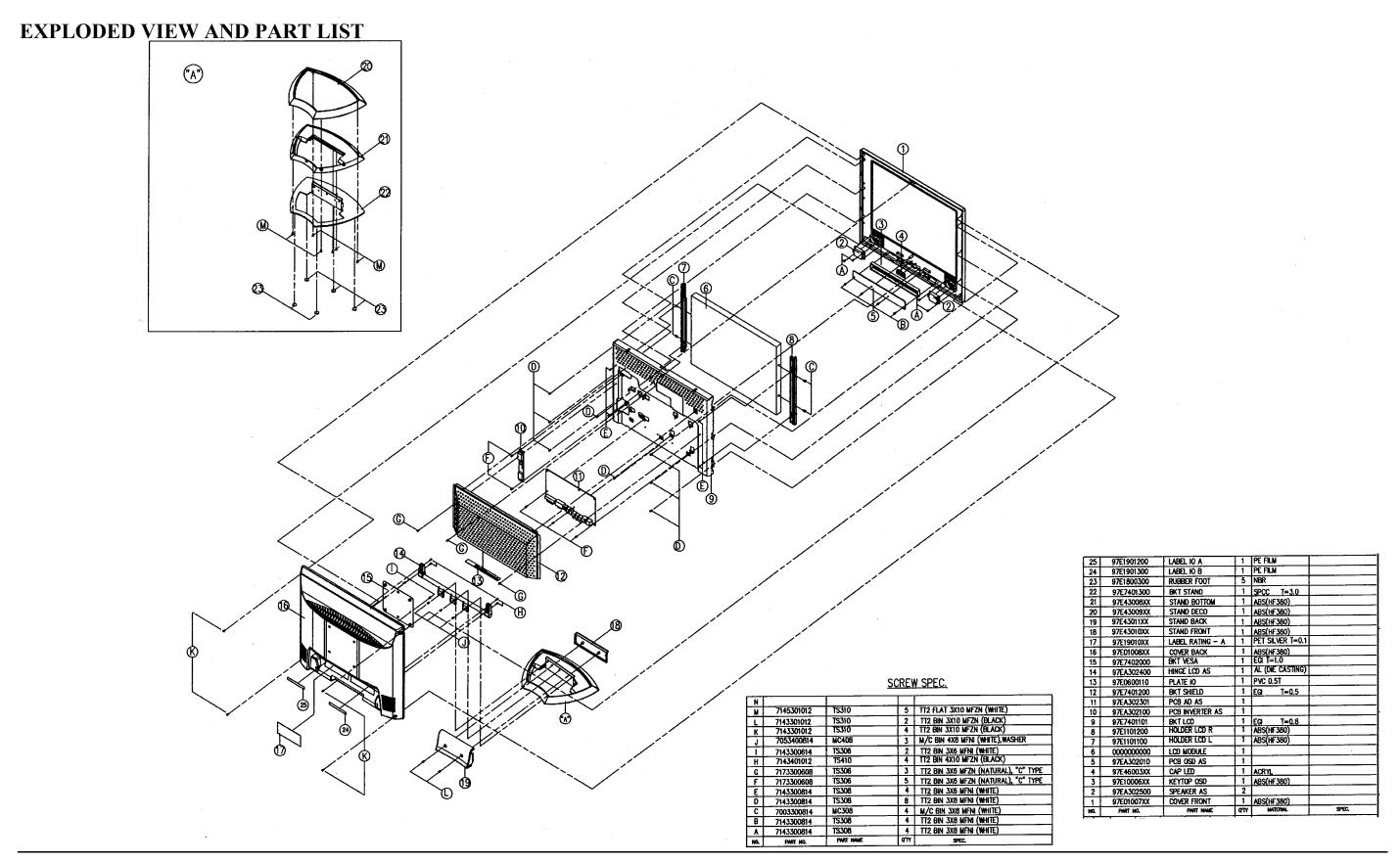

| EXPLODED VIEW & PART LIST                 | 186 |

# **SPECIFICATION**

> Resolution: 17.0 inch SXGA (1280 x 1024 @75Hz)

➤ Color display: 16,777,216 colors

> DPMS (Display Power Management Signaling)

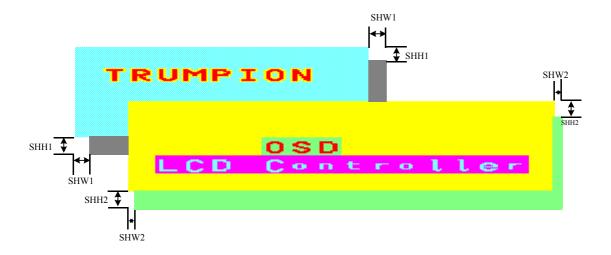

➤ OSD (On Screen Display)

> Auto Configuration: Hot Key

> Speaker [L + R: 3W + 3W = 6W (max)]

DDC 1/2 B: Plug & Play

Model No.: LCT-17HT

# **PANEL: HT17E12-200**

### 1. GENERAL DESCRIPTION

#### 1.1 Introduction

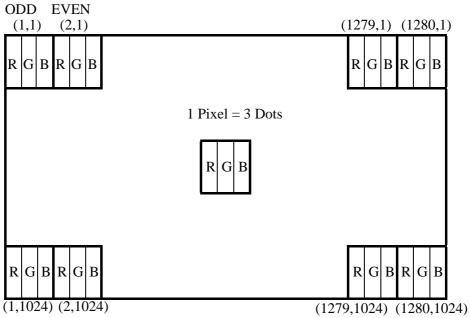

HT17E12-200 is a color active matrix TFT LCD module using amorphous silicon TFT's (Thin Film Transistors) as an active switching devices. This module has a 17.0 inch diagonally measured active area with SXGA resolutions (1280 horizontal by 1024 vertical pixel array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16,194,227 colors. The TFT-LCD panel used for this module is adapted for a low reflection and higher color type.

# 1.2 Features

- ➤ LVDS Interface with 2 pixel / clock

- > High-speed response

- ➤ Low power consumption

- ➤ 6-bit (FRC) color depth, display 16,194,227 colors

- ➤ Incorporated edge type back-light (Four lamps)

- ➤ High luminance and contrast ratio, low reflection and wide viewing angle

- DE (Data Enable) mode

Model No.: LCT-17HT

# 1.3 Applications

- > Desktop Type of PC & Workstation Use

- ➤ Slim-Size Display for Stand-alone Monitor

- Display Terminals for Control System

- Monitors for Process Controller

# 1.4 General Specifications

The followings are general specifications at the model HT17E12-200

<Table 1. General Specifications>

| Parameter           | Specification                                  | Unit   |

|---------------------|------------------------------------------------|--------|

| Active area         | 337.92 (H) × 270.336(V)                        | Mm     |

| Number of pixels    | 1280(H) × 1024(V)                              | pixels |

| Pixel pitch         | $0.264(H) \times 0.264(V)$                     | Mm     |

| Pixel arrangement   | RGB Vertical stripe                            |        |

| Display colors      | 16,194,227                                     | colors |

| Display mode        | Normally White                                 |        |

| Dimensional outline | $358.5(H) \times 296.5(V) \times 17.0(D)$ type | Mm     |

| Weight              | 1900 max.                                      | gram   |

| Back-light          | Top/Bottom edge side 4-CCFL type               |        |

Note: 1. CCFL (Cold Cathode Fluorescent Lamp)

#### 2.0 ABSOLUTE MAXIMUM RATINGS

The followings are maximum values which, if exceed, may cause faulty operation or damage to the unit. The operational and non-operational maximum voltage and current values are listed in Table 2.

<Table 2. Absolute Maximum Ratings> [VSS = GND =0V]

| Parameter               | Symbol            | Min     | Max                  | Unit | Remarks   |

|-------------------------|-------------------|---------|----------------------|------|-----------|

| Power Input Voltage     | $V_{\mathrm{DD}}$ | VSS-0.5 | 6.5                  | V    | Ta=25°C   |

| Logic Input Voltage     | V <sub>IN</sub>   | VSS-0.3 | V <sub>DD</sub> +0.3 | V    | 1 1a-23 C |

| Back-light Lamp Current | $I_{\mathrm{BL}}$ | 3       | 7                    | mA   |           |

| Back-light lamp         | $F_{L}$           | 30      | (80)                 | KHz  |           |

| Frequency               |                   |         |                      |      |           |

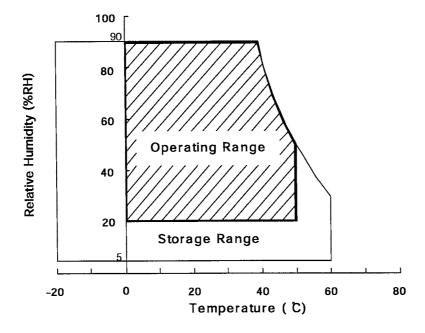

| Operating Temperature   | T <sub>OP</sub>   | 0       | +50                  | °C   | 1)        |

| Storage Temperature     | $T_{ST}$          | -20     | +60                  | °C   | 1)        |

#### Notes:

- 1. Temperature and relative humidity range are shown in the figure below.

- 2. Wet bulb temperature should be 39°C max and no condensation of water.

#### 3.0 ELECTRICAL SPECIFICATIONS

< Table 3. Electrical specifications >  $[Ta = 25 \pm 2^{\circ}C]$

| Parameter                     |                    | Min   | Тур   | Max  | Unit             | Remarks                       |

|-------------------------------|--------------------|-------|-------|------|------------------|-------------------------------|

| Power Supply Voltage          | $V_{DD}$           | 4.5   | 5.0   | 5.5  | V                | Note1                         |

| Power Supply Current          | $I_{DD}$           | -     | 580   | 700  | mA               | Note1                         |

| Permissible Input Ripple      | $V_{RF}$           |       |       | 100  | mV               | $V_{\rm DD} = 5.0 \mathrm{V}$ |

| Voltage                       |                    |       |       |      |                  |                               |

| High Level Differential Input | $V_{\mathrm{IH}}$  |       | -     | +100 | mV               |                               |

| Threshold Voltage             |                    |       |       |      |                  | Vcm                           |

| Low Level Differential Input  | $V_{\rm IL}$       | -100  | -     |      | mV               | = 1.2V  typ                   |

| Threshold Voltage             |                    |       |       |      |                  |                               |

| Back-light Lamp Voltage       | $V_{BL}$           | 690   | 700   | 840  | V <sub>rms</sub> |                               |

| Back-light Lamp Current       | $I_{BL}$           | 3.0   | 6.5   | 7.0  | $mA_{rms}$       |                               |

| Back-light Lamp operating     | $F_{L}$            | 30    | -     | 70   | KHz              | Note 2                        |

| Frequency                     |                    |       |       |      |                  |                               |

| Lown Stort Woltago            |                    |       | 940   | 1170 | V <sub>rms</sub> | 25°C, Note 3                  |

| Lamp Start Voltage            |                    |       | 1340  | 1570 | V <sub>rms</sub> | 0°C, Note 3                   |

| Lamp Life                     |                    | 40000 | 50000 |      | hrs              | $I_{BL} = 6.5 \text{mA}$      |

|                               | $P_{D}$            |       | 2.9   |      | W                | $I_{BL}$ = 6.5mA,             |

| Power Consumption             | $P_{BL}$           |       | 18.2  |      | W                | Note 4                        |

|                               | P <sub>total</sub> |       | 21.1  |      | W                |                               |

#### Notes:

- 1. The supply voltage is measured and specified at the interface connector of LCM. The current draw and power consumption specified is for VDD = 5.0V, Frame rate= 75Hz and Clock frequency = 67.5MHz. Test Pattern of power supply current

- a. Typ: Black pattern

- b. Max: Dot pattern

- 2. The lamp frequency should be selected as different as possible from the horizontal synchronous frequency and its harmonics to avoid interference, which may cause line flow on the display

- 3. The voltage above this value should be applied to the lamps for more than 1 second to start-up. Otherwise the lamps may not be turned on.

- 4. Calculated value for reference (V  $_{BL}$   $\times$   $\,$   $I_{BL})$   $\times$  4 excluding inverter loss.

Model No.: LCT-17HT

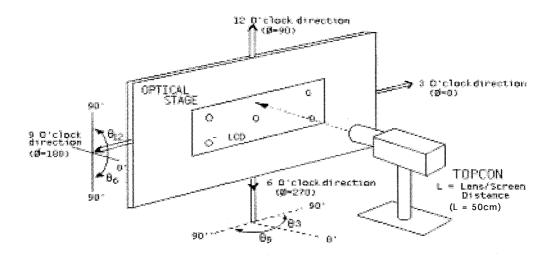

#### 4.0 OPTICAL SPECIFICATIONS

#### 4.1 Overview

The test of Optical specifications shall be measured in a dark room (ambient luminance  $\leq 1$  lux and temperature =  $25\pm2^{\circ}$ C) with the equipment of Luminance meter system (Goniometer system and TOPCON BM-5) and test unit shall be located at an approximate distance 50cm from the LCD surface at a viewing angle of  $\theta$  and  $\phi$  equal to  $0^{\circ}$ . We refer to  $\theta\phi=0$  (= $\theta$ 3) as the 3 o'clock direction (the "right"),  $\theta\phi=90$  (= $\theta$ 12) as the 12 o'clock direction ("upward"),  $\theta\phi=180$  (= $\theta$ 9) as the 9 o'clock direction ("left") and  $\theta\phi=270$  (= $\theta$ 6) as the 6 o'clock direction ("bottom"). While scanning  $\theta$  and/or  $\phi$ , the center of the measuring spot on the display surface shall stay fixed. The measurement shall be executed after 30 minutes warm-up period. VDD shall be 5.0V +/- 10% at 25°C. Optimum viewing angle direction is 6 o'clock.

4.2 Optical Specifications [VDD=5.0V, Frame rate=60Hz, Clock=54MHz, IBL = 6.5mA, Ta = 25±2°Q

| Param                    | neter        |          | Symbol        | Condition              | Min   | Тур   | Max   | Unit              | Remark |  |

|--------------------------|--------------|----------|---------------|------------------------|-------|-------|-------|-------------------|--------|--|

|                          | Ша           | rizontal | Θ3            |                        | 75    | 80    | -     | Deg               |        |  |

|                          | по           | HZOHIAI  | $\Theta_9$    | CR>10                  | 75    | 80    | -     | Deg               |        |  |

|                          | Va           | rtical   | $\Theta_{12}$ | CK/10                  | 60    | 65    | -     | Deg               |        |  |

| Viewing                  | Ve           | iticai   | $\Theta_6$    |                        | 60    | 65    | -     | Deg               | Note 1 |  |

| Angle                    | Ца           | rizontal | $\Theta_3$    |                        | 80    | 85    | -     | Deg               | Note 1 |  |

|                          | по           | HZOHIAI  | $\Theta_9$    | CR>5                   | 80    | 85    | -     | Deg               |        |  |

|                          | Ve           | rtical   | $\Theta_{12}$ | CK>3                   | 70    | 75    | -     | Deg               |        |  |

|                          |              | iticai   | $\Theta_6$    |                        | 70    | 75    | -     | Deg               |        |  |

| Luminance con            | ntrast       | ratio    | CR            |                        | 350   | 430   | -     |                   | Note 2 |  |

| Luminance of             | white        | )        | $Y_{W}$       |                        | 200   | 250   | -     | cd/m <sup>2</sup> | Note 3 |  |

| White luminar uniformity | nce          |          | ⊿ Y           |                        | -     | -     | 1.2   |                   | Note 4 |  |

|                          |              | XX //    | Wx            |                        | 0.270 | 0.300 | 0.330 |                   |        |  |

|                          |              | White    | Wy            | $\Theta$ = $0^{\circ}$ | 0.305 | 0.335 | 0.365 |                   |        |  |

| D                        |              | Dad      | Rx            |                        | 0.599 | 0.629 | 0.659 |                   |        |  |

| Reproduction of color    |              | Red      | Ry            | (Center)<br>Normal     | 0.324 | 0.354 | 0.384 |                   | Note 5 |  |

| of color                 |              | Green    | Gx            | Viewing                | 0.257 | 0.287 | 0.317 |                   | Note 5 |  |

|                          |              | Green    | Gy            | Angle                  | 0.568 | 0.598 | 0.628 |                   |        |  |

|                          |              | Blue     | Bx            | Aligic                 | 0.115 | 0.145 | 0.175 |                   |        |  |

|                          |              |          | Ву            |                        | 0.073 | 0.103 | 0.133 |                   |        |  |

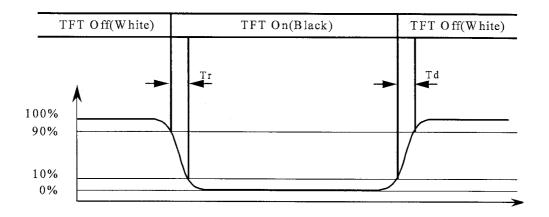

| Dagnonga timo            | Dannana tima |          | Tr            |                        | -     | 5     | 30    | msec              | Note 6 |  |

| Kesponse time            | esponse time |          | Td            |                        | -     | 15    | ] 30  | msec              | Note 0 |  |

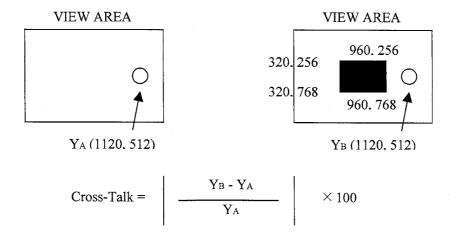

| Cross talk               |              |          | CT            |                        | -     | -     | 2.0   | %                 | Note 7 |  |

Model No.: LCT-17HT

#### Note:

- 1. Viewing angle is the angle at which the contrast ratio is greater than 10. The viewing are determined for the horizontal or 3, 9 o'clock direction and the vertical or 6, 12 o'clock direction with respect to the optical axis which is normal to the LCD surface.

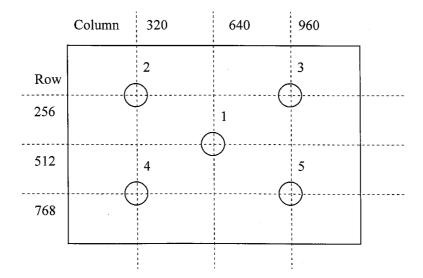

- 2. Contrast measurements shall be made at viewing angle of  $\theta$ = 0° and at the center of the LCD surface. Luminance shall be measured with all pixels in the view field set first to white, then to the dark (black) state. (See FIGURE 1 shown in Appendix) Luminance Contrast Ratio (CR) is defined mathematically.

CR = <u>Luminance when displaying a white raster</u> Luminance when displaying a black raster

- 3. Center Luminance of white is defined as the LCD surface. Luminance shall be measured with all pixels in the view field set first to white. This measurement shall be taken at the locations shown in FIGURE 2 for a total of the measurements per display.

- 4. The White luminance uniformity on LCD surface is then expressed as :  $\triangle Y = Maximum$  Luminance of five points / Minimum Luminance of five points (See FIGURE 2 shown in appendix).

- 5. The color chromaticity coordinates specified in Table 4. shall be calculated from the spectral data measured with all pixels first in red, green, blue and white. Measurements shall be made at the center of the panel.

- 6. The electro-optical response time measurements shall be made as FIGURE 3 shown in Appendix by switching the "data" input signal ON and OFF. The times needed for the luminance to change from 10% to 90% is Td, and 90% to 10% is Tr.

- 7. Cross-Talk of one area of the LCD surface by another shall be measured by comparing the luminance (Y<sub>A</sub>) of a 25mm diameter area, with all display pixels set to a gray level, to the luminance (Y<sub>B</sub>) of that same area when any adjacent area is driven dark. (See FIGURE 4 shown in Appendix).

Model No.: LCT-17HT

# 5.0 INTERFACE CONNECTION

5.1 Electrical Interface Connection

CN11: Module Side Connector : FI-XB30S-HF (JAE) or Equivalent

User Side Connector : FI-X30H-HF (JAE) or equivalent

| Pin No | Symbol  | Function                 | Remark |

|--------|---------|--------------------------|--------|

| 1      | RXO0-   | LVDS ODD 0 – SIGNAL      |        |

| 2      | RXO0+   | LVDS ODD 0 + SIGNAL      |        |

| 3      | RXO1-   | LVDS ODD 1 – SIGNAL      |        |

| 4      | RXO1+   | LVDS ODD 1 + SIGNAL      |        |

| 5      | RXO2-   | LVDS ODD 2 – SIGNAL      |        |

| 6      | RXO2+   | LVDS ODD 2 + SIGNAL      |        |

| 7      | GND     | GROUND                   |        |

| 8      | RXOCLK- | LVDS ODD CLOCK – SIGNAL  |        |

| 9      | RXOCLK+ | LVDS ODD CLCOK + SIGNAL  |        |

| 10     | RXO3-   | LVDS ODD 3 – SIGNAL      |        |

| 11     | RXO3+   | LVDS ODD 3 + SIGNAL      |        |

| 12     | RXE0-   | LVDS EVEN 0 – SIGNAL     |        |

| 13     | RXE0+   | LVDS EVEN 0 + SIGNAL     |        |

| 14     | GND     | GROUND                   |        |

| 15     | RXE1-   | LVDS EVEN 1 – SIGNAL     |        |

| 16     | RXE1+   | LVDS EVEN 1 + SIGNAL     |        |

| 17     | GND     | GROUND                   |        |

| 18     | RXE2-   | LVDS EVEN 2 – SIGNAL     |        |

| 19     | RXE2+   | LVDS EVEN 2 + SIGNAL     |        |

| 20     | RXECLK- | LVDS EVEN CLOCK – SIGNAL |        |

| 21     | RXECLK+ | LVDS EVEN CLOCK + SIGNAL |        |

| 22     | RXE3-   | LVDS EVEN 3 – SIGNAL     |        |

| 23     | RXE3+   | LVDS EVEN 3 + SIGNAL     |        |

| 24     | GND     | GROUND                   |        |

| 25     | NC      | NO CONECTION             |        |

| 26     | DE      | NO CONECTION             |        |

| 27     | NC      | NO CONECTION             |        |

| 28     | VDD     |                          |        |

| 29     | VDD     | POWER SUPPLY (+5.0V)     |        |

| 30     | VDD     |                          |        |

Model No.: LCT-17HT

# 5.2 LVDS Interface (Tx: THC63LVDF83A or Equivalent)

|           | Input signal | Trans  | mitter | Inter          | face           | FI-X30S-HF | Remark |

|-----------|--------------|--------|--------|----------------|----------------|------------|--------|

|           |              | Pin No | Pin No | System (Tx)    | TFT-LCD (Rx)   | Pin No.    |        |

|           | OR0          | 51     |        |                |                |            |        |

|           | OR1          | 52     |        |                |                |            |        |

|           | OR2          | 54     | 10     | OUTO           | DVO0           | 1          |        |

|           | OR3          | 55     | 48     | OUT0-<br>OUT0+ | RXO0-<br>RXO0+ | 1 2        |        |

|           | OR4          | 56     | 47     | 0010+          | KXU0+          | 2          |        |

|           | OR5          | 3      |        |                |                |            |        |

|           | OG0          | 4      |        |                |                |            |        |

|           | OG1          | 6      |        |                |                |            |        |

|           | OG2          | 7      |        |                |                |            |        |

|           | OG3          | 11     | 46     | OLUT1          | DVO1           | 2          |        |

|           | OG4          | 12     | 46     | OUT1-          | RXO1-          | 3          |        |

|           | OG5          | 14     | 45     | OUT1+          | RXO1+          | 4          |        |

|           | OB0          | 15     |        |                |                |            |        |

| S         | OB1          | 19     |        |                |                |            |        |

| ODDTADS   | OB2          | 20     |        |                |                |            |        |

| DD 1      | OB3          | 22     |        |                |                |            |        |

| 0         | OB4          | 23     | 12     | OLUTA          | DVO2           | _          |        |

|           | OB5          | 24     | 42     | OUT2-          | RXO2-          | 5          |        |

|           | HSYNC        | 27     | 41     | OUT2+          | RXO2+          | 6          |        |

|           | VSYNC        | 28     |        |                |                |            |        |

|           | DE           | 30     |        |                |                |            |        |

|           | MCLK         | 31     | 40     | CLKOUT-        | RXO CLK-       | 8          |        |

|           |              |        | 39     | CLKOUT+        | RXO CLK+       | 9          |        |

|           | OR6          | 50     |        |                |                |            |        |

|           | OR7          | 2      |        |                |                |            |        |

|           | OG6          | 8      | 20     | OLUTA:         | DVO2           | 10         |        |

|           | OG7          | 10     | 38     | OUT3+          | RXO3-          | 10         |        |

|           | OB6          | 16     | 37     | OUT3-          | RXO3+          | 11         |        |

|           | OB7          | 18     |        |                |                |            |        |

|           | RSVD         | 25     |        |                |                |            |        |

|           | ER0          | 51     |        |                |                |            |        |

|           | ER1          | 52     |        |                |                |            |        |

| EVEN LVDS | ER2          | 54     | 40     | OUTO           | DVE            | 12         |        |

| N         | ER3          | 55     | 48     | OUT0-          | RXE0-          | 12         |        |

| 3VE       | ER4          | 56     | 47     | OUT0+          | RXE0+          | 13         |        |

|           | ER5          | 3      |        |                |                |            |        |

|           | EG0          | 4      |        |                |                |            |        |

Model No.: LCT-17HT Version: 1.0

|           | Input signal | Trans  | mitter | Inter       | face              | FI-X30S-HF | Remark |

|-----------|--------------|--------|--------|-------------|-------------------|------------|--------|

|           |              | Pin No | Pin No | System (Tx) | TFT-LCD (Rx)      | Pin No.    |        |

|           | EG1          | 6      |        |             |                   |            |        |

|           | EG2          | 7      |        |             |                   |            |        |

|           | EG3          | 11     | 46     | OUT1-       | RXE1-             | 15         |        |

|           | EG4          | 12     | 45     | OUT1+       | RXE1-             | 16         |        |

|           | EG5          | 14     | 43     | 0011+       | KAE1 <sup>+</sup> | 10         |        |

|           | EB0          | 15     |        |             |                   |            |        |

|           | EB1          | 19     |        |             |                   |            |        |

|           | EB2          | 20     |        |             |                   |            |        |

|           | EB3          | 22     |        |             |                   |            |        |

|           | EB4          | 23     | 42     | OUT2 –      | RXE2-             | 18         |        |

| EVEN LVDS | EB5          | 24     | 41     | OUT2+       | RXE2+             | 19         |        |

| Z         | HSYNC        | 27     | 71     | 00121       | KAE2              | 1)         |        |

| EVE       | VSYNC        | 28     |        |             |                   |            |        |

|           | DE           | 30     |        |             |                   |            |        |

|           | MCLK         | 31     | 40     | CLKOUT-     | RXE CLK-          | 20         |        |

|           | WICLK        | 31     | 39     | CLKOUT+     | RXE CLK+          | 21         |        |

|           | ER6          | 50     |        |             |                   |            |        |

|           | ER7          | 2      |        |             |                   |            |        |

|           | EG6          | 8      | 38     | OUT3+       | RXE3-             | 22         |        |

|           | EG7          | 10     | 37     | OUT3 -      | RXE3+             | 23         |        |

|           | EB6          | 16     | 31     | 0013-       | KAEJ              | 23         |        |

|           | EB7          | 18     |        |             |                   |            |        |

|           | RSVD         | 25     |        |             |                   |            |        |

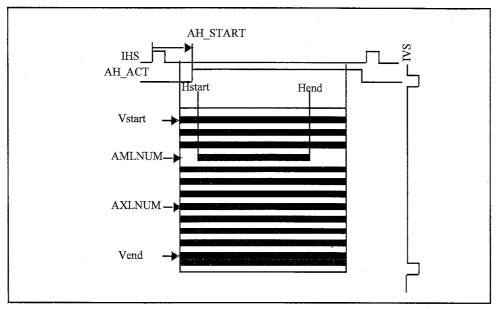

#### 5.3 Data Input Format

Display Position of Input Data (V-H)

5.4 Back-light Interface Connection

CN21, 22, 23, 24: Module side connector : BHSR-02VS-1 (JST)

> User side connector : SM02B-BHSS-1-TB (JST) or equivalent

|        | Pin No   | INDLT | Color         | Function     |

|--------|----------|-------|---------------|--------------|

| Pin No | FIII INO | INPUT | Color         | Function     |

| 1      |          | НОТ   | Pink & White  | High voltage |

| 2      |          | COLD  | Black & White | Ground       |

Model No.: LCT-17HT

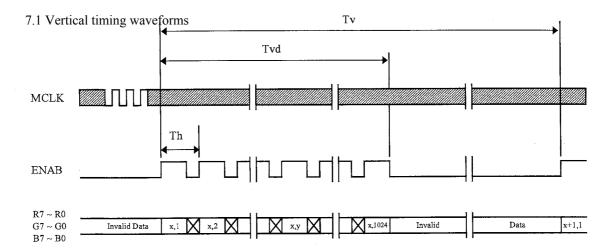

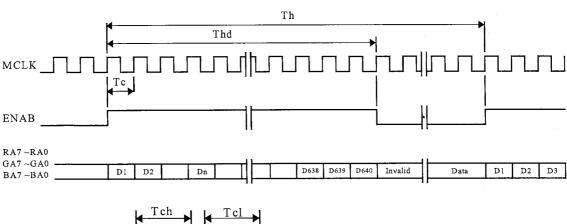

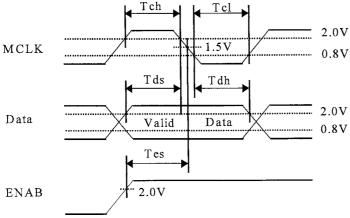

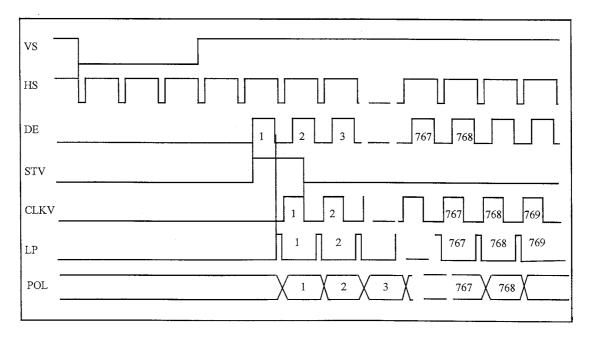

#### 6.0 SIGNAL TIMING SPECIFICATION

6.1 The HT17E12-200 is operated by the only DE (Data enable) mode (LVDS Transmitter Input)

|        | Item                 | Symbols | Min   | Тур   | Max  | Unit   |

|--------|----------------------|---------|-------|-------|------|--------|

|        | Frequency            | 1/Tc    | 40    | 54    | 68   | MHz    |

| Clock  | High Time            | Tch     | 5     | 1     | 1    | ns     |

|        | Low Time             | Tcl     | 5     | 1     | 1    | ns     |

| Data   | Setup Time           | Tds     | 4     | 1     | 1    | ns     |

| Data   | Hold Time            | Tdh     | 4     | 1     | 1    | ns     |

| Data 1 | Enable Setup Time    | Tes     | 4     | 1     | 1    | ns     |

|        | Frame Period         | Tv      | 1032  | 1066  | 1536 | lines  |

|        | rianie renou         |         | 13.33 | 16.67 | 1    | msec   |

| Verti  | cal Display Period   | Tvd     | ı     | 1024  | 1    | lines  |

| One Li | ine Scanning Period  | Th      | 672   | 844   | 1022 | clocks |

| Horizo | ontal Display Period | Thd     | 640   | 640   | 640  | clocks |

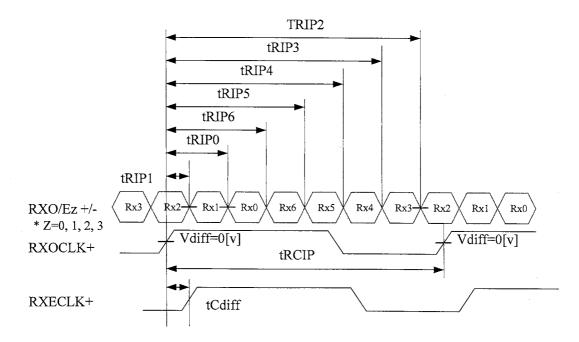

# 6.2 LVDS Rx interface timing parameter

The specification of the LVDS Rx interface timing parameter is shown in Table 4.

< Table 4. LVDS Rx Interface Timing Specification>

|                |        | <u> </u>      |           |               |      |        |

|----------------|--------|---------------|-----------|---------------|------|--------|

| Item           | Symbol | Min           | Тур       | Max           | Unit | Remark |

| CLKIN Period   | tRCIP  | 14.7          | 18.5      | -             | nsec |        |

| CLK Difference | tCdiff | -tRCIP*(3/7)  | 0         | +tRCIP*(3/7)  | nsec |        |

| Input Data 0   | tRIP1  | -0.4          | 0         | +0.4          | nsec |        |

| Input Data 1   | tRIP0  | 1*tRICP/7-0.4 | 1*tRICP/7 | 1*tRICP/7+0.4 | nsec |        |

| Input Data 2   | tRIP6  | 2*tRICP/7-0.4 | 2*tRICP/7 | 2*tRICP/7+0.4 | nsec |        |

| Input Data 3   | tRIP5  | 3*tRICP/7-0.4 | 3*tRICP/7 | 3*tRICP/7+0.4 | nsec |        |

| Input Data 4   | tRIP4  | 4*tRICP/7-0.4 | 4*tRICP/7 | 4*tRICP/7+0.4 | nsec |        |

| Input Data 5   | tRIP3  | 5*tRICP/7-0.4 | 5*tRICP/7 | 5*tRICP/7+0.4 | nsec |        |

| Input Data 6   | tRIP2  | 6*tRICP/7-0.4 | 6*tRICP/7 | 6*tRICP/7+0.4 | nsec |        |

Model No.: LCT-17HT

\* Vdiff = (RXO/Ez+)-(RXO/Ez-), ...., (RXO/ECLK+)-(RXO/ECLK-)

Model No.: LCT-17HT

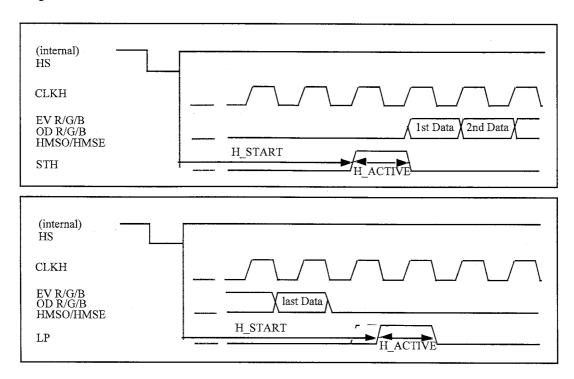

#### 7.0 SIGNAL TIMING WAVEFORMS OF INTERFACE SIGNAL

# 7.2 Horizontal Timing Waveforms

Model No.: LCT-17HT

# 8.0 INPUT SIGNAL, BASIC DISPLAY COLORS & GRAY SCALE OF COLOR

| Colors &   | r Gray             | . G1 17 | ·, .    | <b>D</b> 1 <b>X</b> 1. | Red     |         | 1.77.1 |     | OL      |           | <u> </u> |         |         | n data   |         | 01       |          |   |                                    |   | Rlue     | - data   |   |   |   |  |

|------------|--------------------|---------|---------|------------------------|---------|---------|--------|-----|---------|-----------|----------|---------|---------|----------|---------|----------|----------|---|------------------------------------|---|----------|----------|---|---|---|--|

| Scale      | x Gray             | D.7     | D.      | D.5                    | 1       |         | R2     | D 1 | DΛ      | G7        |          |         |         |          |         |          |          |   | B1ue data  B7 B6 B5 B4 B3 B2 B1 B0 |   |          |          |   |   |   |  |

| -          | Black              | R7<br>0 | R6<br>0 | R5                     | R4<br>0 | R3<br>0 | 0      | R1  | R0<br>0 | 0         | G6<br>0  | G5<br>0 | G4<br>0 | G3<br>0  | G2<br>0 | G1<br>0  | G0<br>0  | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | Blue               | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

|            | Green              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Basic      | Cyan               | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

|            | Red                | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | Magenta            | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

|            | Yellow             | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | White              | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

|            | Black              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | <b>A</b>           | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Gray       | Darker             | 0       | 0       | 0                      | 0       | 0       | 0      | 1   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Scale      | <b>A</b>           |         |         |                        | 1       | 1       |        |     |         |           |          |         |         | 1        |         |          |          |   |                                    |   |          | 1        |   |   |   |  |

| Of Red     | ▼                  |         | 1       | 1                      | 1       | ,       | 1      |     | 1       |           |          | 1       |         | <b></b>  | 1       |          |          |   |                                    | 1 |          | <b></b>  | 1 |   |   |  |

|            | Brighter<br>▼      | 1       | 1       | 1                      | 1       | 1       | 1      | 0   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            |                    | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| -          | Red                | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | Black              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Gray       | <b>▲</b><br>Darker | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 1        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Scale      | Darker<br>▲        | -       |         |                        | 1       | `       |        |     | Ů       |           | Ü        |         |         | <u> </u> |         | 1        | Ů        |   | Ů                                  | Ů |          | <u> </u> |   | Ů |   |  |

| Of         | ▼                  |         |         |                        | 1       | ļ       |        |     |         | <br> <br> |          |         |         |          |         |          | <b>↓</b> |   |                                    |   |          |          |   |   |   |  |

| Green      | Brighter           | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 0        | 1        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | ▼                  | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | Green              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | Black              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

|            | <b>A</b>           | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 1 |  |

| Gray       | Darker             | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 1 | 0 |  |

| Scale      | <b>A</b>           |         |         |                        | 1       |         |        |     |         |           |          |         |         | <b>1</b> |         |          |          |   |                                    |   |          | 1        |   |   |   |  |

| Of<br>Blue | ▼<br>Brighter      | 0       |         |                        | 1       | ,       |        | 0   | _       | 0         | 0        |         | 0       | <b>↓</b> | Ι ,     | 0        | 0        |   | 1                                  |   | 1        | ↓<br>    | 1 | 0 | 1 |  |

| Blue       | ▼                  | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 1 | 1                                  | 1 | 1        | 1        | 1 | 0 | 0 |  |

|            | Blue               | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

|            | Black              | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 0 |  |

| Gray       | <b>A</b>           | 0       | 0       | 0                      | 0       | 0       | 0      | 0   | 1       | 0         | 0        | 0       | 0       | 0        | 0       | 0        | 1        | 0 | 0                                  | 0 | 0        | 0        | 0 | 0 | 1 |  |

| Scale      | Darker             | 0       | 0       | 0                      | 0       | 0       | 0      | 1   | 0       | 0         | 0        | 0       | 0       | 0        | 0       | 1        | 0        | 0 | 0                                  | 0 | 0        | 0        | 0 | 1 | 0 |  |

| Of         | <b>A</b>           |         |         |                        | 1       |         |        |     |         | <u>†</u>  |          |         |         |          |         |          |          |   |                                    |   | <b>↑</b> |          |   |   |   |  |

| White      | ▼                  |         |         |                        |         | ļ       |        |     |         | <u></u>   |          |         |         |          |         | <b>↓</b> |          |   |                                    |   |          |          |   |   |   |  |

| &          | Brighter           | 1       | 1       | 1                      | 1       | 1       | 1      | 0   | 1       | 1         | 1        | 1       | 1       | 1        | 1       | 0        | 1        | 1 | 1                                  | 1 | 1        | 1        | 1 | 0 | 1 |  |

| Black      | ▼                  | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 0       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 0        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 0 |  |

|            | White              | 1       | 1       | 1                      | 1       | 1       | 1      | 1   | 1       | 1         | 1        | 1       | 1       | 1        | 1       | 1        | 1        | 1 | 1                                  | 1 | 1        | 1        | 1 | 1 | 1 |  |

Model No.: LCT-17HT

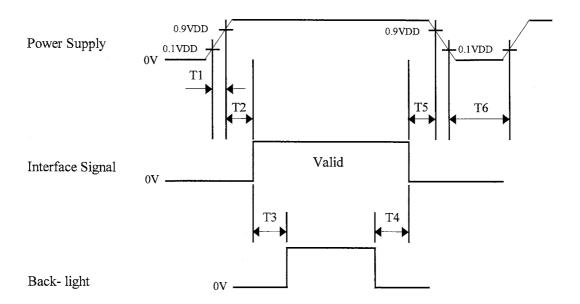

#### 9.0 POWER SEQUENCE

To prevent a latch-up or DC operation of the LCD module, the power on/off sequence should be as shown in below.

- $> 0 < T1 \le 10 \text{ ms}$

- $\triangleright$  20ms < T2  $\leq$  50 ms

- $\gt$  500 ms  $\leq$  T3

- $\gt$  100 ms  $\leq$  T4

- > 0 < T5  $\leq$  50 ms

- $\triangleright$  1 sec ≤ T6

#### Notes:

- 1. When the power supply VDD is 0V, Keep the level of input signals on the low or keep high impedance.

- 2. Do not keep the interface signal high impedance when power is on.

- 3. Back Light must be turn on after power for logic and interface signal are valid.

Model No.: LCT-17HT

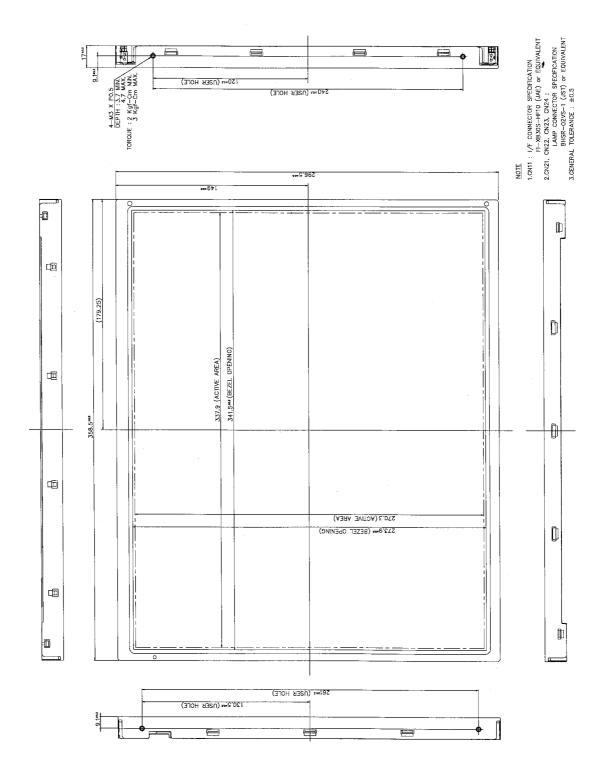

#### 10.0 MECHANICAL CHARACTERSTICS

#### 10.1 Dimensional Requirement

FIGURE 6 shown in appendix shows mechanical outlines for the model HT17E12-200. Other parameter are shown in Table 5.

<Table 5. Dimensional Parameter>

| Parameter           | Specification                                                                        | Unit   |

|---------------------|--------------------------------------------------------------------------------------|--------|

| Dimensional outline |                                                                                      |        |

| Horizontal          | $358.5 \pm 0.5$                                                                      |        |

| Vertical            | $296.5 \pm 0.5$                                                                      | Mm     |

| Thickness           | $17.0 \pm 0.5$                                                                       |        |

| Weight              | 1900 max                                                                             | Gram   |

| Active area         | 337.92 (h) x 270.336 (v)                                                             | Mm     |

| Pixel pitch         | 0.264 (h) x 0.264 (v)                                                                | Mm     |

| Number of pixels    | $1280 \text{ (h)} \times 1024 \text{ (v)} (1 \text{ pixel} = R + G + B \text{ dot})$ | Pixels |

| Back-light          | Top/bottom edge 4-CCFL type                                                          |        |

#### 10.2 Mounting

See FIGURE 5 shown in appendix

#### 10.3 Anti-Glare and Polarizer Hardness.

The surface of the LCD has an anti-glare coating to minimize reflection and a coating to reduce scratching.

#### 10.4 Light Leakage

There shall not be visible light from the back-lighting system around the edges of the screen as seen from a distance 50[cm] from the screen with an overhead light level of 350[lux].

The manufacture shall furnish limit samples of the panel showing the lightest leakage acceptable.

Model No.: LCT-17HT

# 11.0 RELIABILITY TEST

The Reliability test items and its conditions are shown in below.

<Table 6. Reliability Test Parameter>

| No | Test Items                                      | Conditions                                                      |                                       |  |  |

|----|-------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|--|--|

| 1  | High temperature storage test                   | $Ta = 60^{\circ}C, 240^{\circ}$                                 | ) hrs                                 |  |  |

| 2  | Low temperature storage test                    | $Ta = -20^{\circ}C$ , 240 hrs                                   |                                       |  |  |

| 3  | High temperature & high humidity operation test | Ta = 50°C, 80 %RH, 240 hrs                                      |                                       |  |  |

| 4  | High temperature operation test                 | $Ta = 50^{\circ}C$ , 240 hrs                                    |                                       |  |  |

| 5  | Low temperature operation test                  | $Ta = 0^{\circ}C$ , 240 hrs                                     |                                       |  |  |

| 6  | Thermal shock                                   | Ta = $-20^{\circ}$ C $\leftrightarrow$ 60°C (30 min), 100 cycle |                                       |  |  |

|    |                                                 | Frequency                                                       | : 10 ~ 300 Hz, Sweep rate 30min       |  |  |

| 7  | Vibration test (non-operating)                  | Gravity/AMP                                                     | : 1.5G                                |  |  |

|    |                                                 | Period                                                          | : ±X, ±Y, ±Z 30min                    |  |  |

| 8  | Shock test (non-operating)                      | Gravity                                                         | : 70G                                 |  |  |

|    |                                                 | Pulse width                                                     | : 11ms, sine wave                     |  |  |

|    |                                                 |                                                                 | ± X, ± Y, ± Z Once for each direction |  |  |

| 0  | Electrostatic discharge test                    | Air                                                             | : 150 pF, 330Ω, 15KV                  |  |  |

| 9  | Electrostatic discharge test                    | Contact                                                         | : 150 pF, 330Ω, 8KV                   |  |  |

Model No.: LCT-17HT Version: 1.0

#### 12.0 HANDLING & CAUTIONS

#### 12.1 Cautions when taking out the module

➤ Pick the pouch only, when taking out module from a shipping package.

#### 12.2 Cautions for handling the module

- As the electrostatic discharges may break the LCD module, handle the LCD module with care. Peel a protection sheet off from the LCD panel surface as slowly as possible.

- As the LCD panel and back-light element are made from fragile glass material, impulse and pressure to the LCD module should be avoided.

- As the surface of the polarizer is very soft and easily scratched, use a soft dry-cloth without chemicals for cleaning.

- > Do not pull the interface connector in or out while the LCD module is operating.

- > Put the module display side down on a flat horizontal plane.

- ➤ Handle connectors and cables with care.

#### 12.3 Cautions for the operation

- ➤ When the module is operating, do not lose LVDS signals. If any one of these signals were lost, the LCD panel would be damaged.

- Obey the supply voltage sequence. If the wrong sequences were applied, the module would be damaged.

#### 12.4 Cautions for the atmosphere

- Dewdrop atmosphere should be avoided.

- > Do not store and/or operate the LCD module in a high temperature and/or humidity atmosphere. Storage in an electro-conductive polymer-packing pouch and under relatively low temperature atmosphere is recommended.

#### 12.5 Cautions for the module characteristics

- > Do not apply fixed pattern data signal to the LCD module at aging time.

- > Applying fixed pattern for a long time may cause image sticking.

#### 12.6 Other cautions

- ➤ Do not disassemble and/or re-assemble LCD module.

- > Do not re-adjust variable resistor or switch etc.

- ➤ When returning the module for repair or etc, please pack the module not to be broken. We recommend on using the original shipping packages.

#### 14.0 APPENDIX

Figure 1. Measurement Set Up

Figure 2. Average Luminance Measurement Locations & Uniformity Measurement Locations.

Model No.: LCT-17HT

Figure 3. Response Time Testing

Figure 4. Cross Modulation Test Description

#### Where:

$Y_A$  = Initial luminance of measured area (cd/m<sup>2</sup>)

$Y_B$  = Subsequent luminance of measured area (cd/m<sup>2</sup>)

The location measured will be exactly the same in both patterns.

Model No.: LCT-17HT

Figure 5. TFT-LCD Module Outline Dimensions (Front View)

Model No.: LCT-17HT

0

**( ©** ф 0 (0) 101,35\*1 **(3)** CN21

Figure 6. TFT-LCD Module Outline Dimensions (Rear view)

¥ | |

₩ 🕀 🍪

0

Model No.: LCT-17HT

**©**

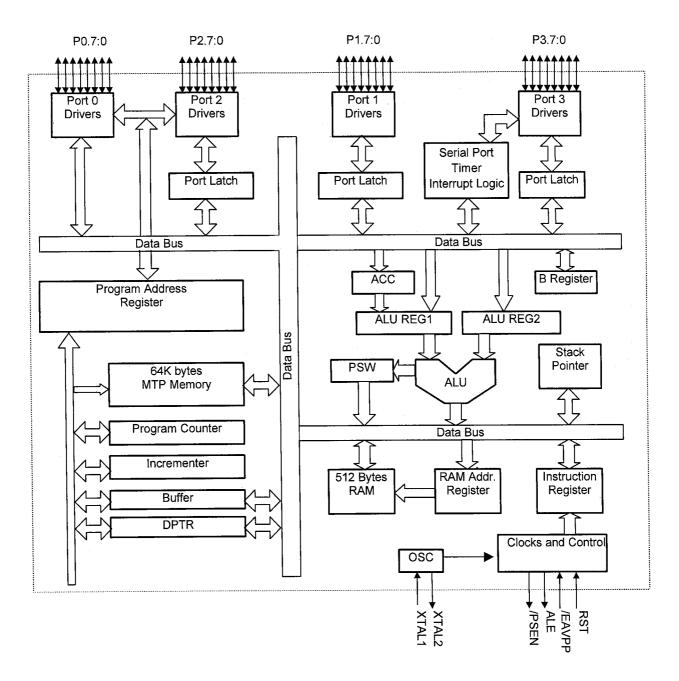

# 8 BIT MTP MICROCONTROLLER

#### 1.0 FEATURES

- > 8051 instruction set compatible 8-bit microcontroller

- ➤ 8051/8052 compatible pinout

- $\triangleright$  Complete static design, wide range of operation frequency from 1 ~ 40 MHz

- > Large on-chip memory

- 64K bytes built-in Multiple Times Programmable ROM (MTP-ROM) program memory

- 512 bytes on-chip SRAM, expandable external 64K bytes address space

- Dual Data Pointer

- Four 8-bit bi-directional I/O ports

- ➤ 6 interrupts including 2 external sources

- ➤ One full-duplex serial UART ports compatible with standard 8052

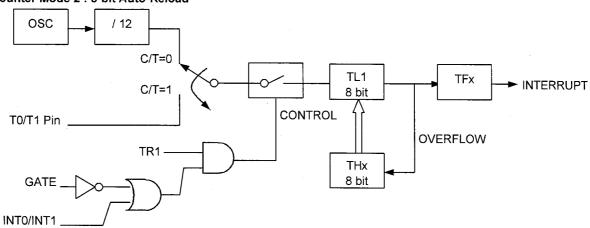

- ➤ Three 16 bit timer/counters

- > On chip oscillator for crystal

- Software Power-Down mode, supports Idle mode and Power Down mode for less power consumption

- > ROM Code Protection

- ➤ 4.5V~5.5V operation voltage, 12V programming voltage

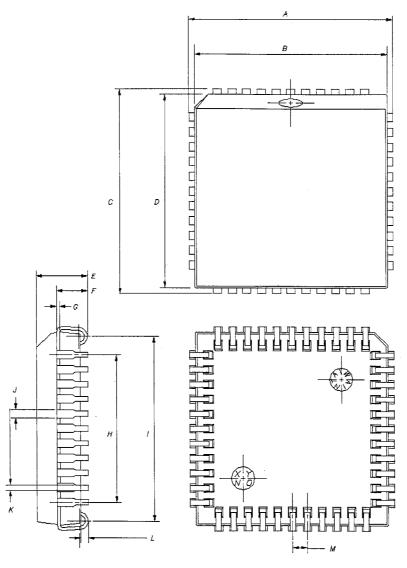

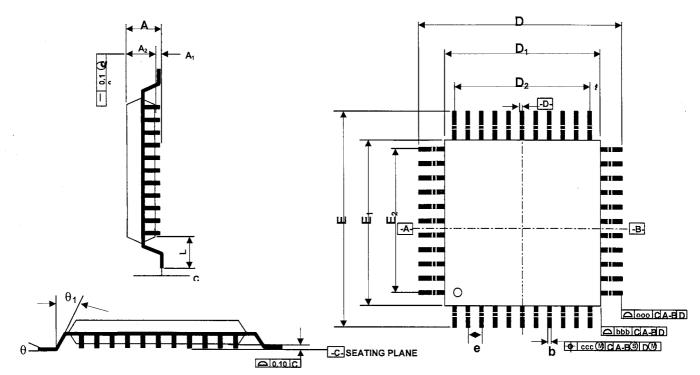

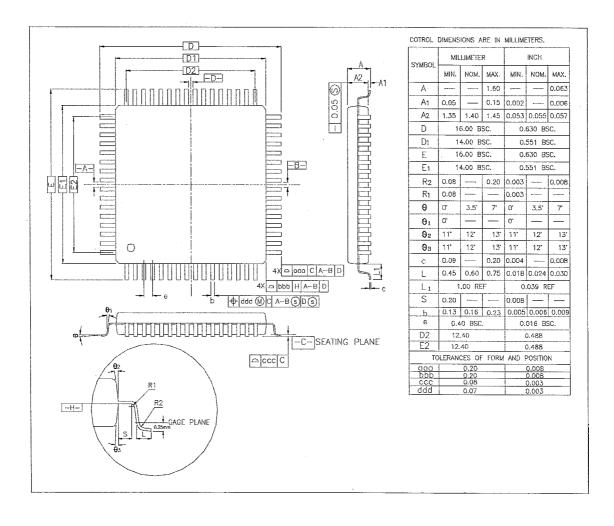

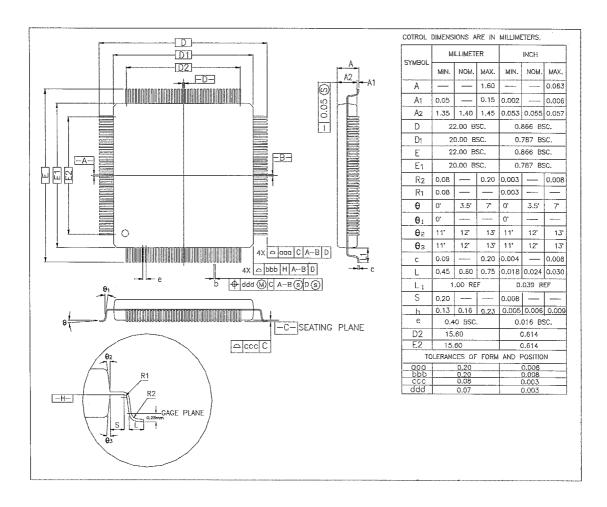

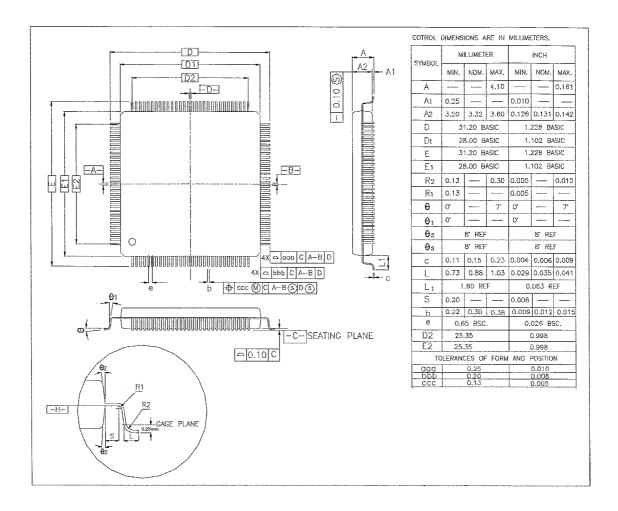

- > 44-pin PLCC or QFP package

#### 1.1 General Description

The M6759 is an 8032/8052 instruction compatible 8-bit microcontroller with MTP Flash ROM for firmware updating. By combining a versatile 8-bit CPU with MTP-Flash, this device provides whole microcontroller system on one chip and still remains the feasibility for general control systems in a variety of applications. Furthermore, user-defined security registers can protect the firmware after the code is ready.

The M6759 contains the following:

- a. A non-volatile 64K bytes Multiple Times Programmable ROMprogram memory.

- b. A volatile 512 bytes read/write data memory

- c. Four 8-bit I/O ports, two 16-bit timer/event counters (identical to the timers of the 80C51)

- d. A 16-bit timer (identical to the Timer 2 of the 8052).

- e. A multi-source two-priority-level nested interrupt structure.

- f. One serial interface (UART) and

- g. An on-chip oscillator.

Model No.: LCT-17HT

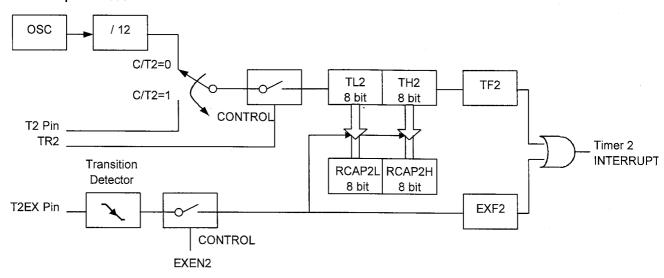

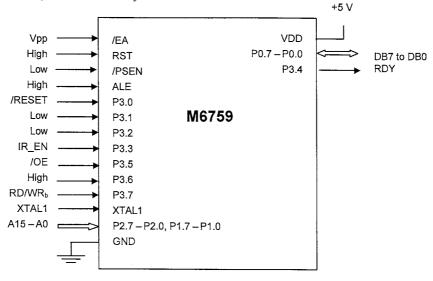

#### 1.2 Block Diagram

Model No.: LCT-17HT

# 2.0 PIN Description

#### 2.1 Pinout Diagram

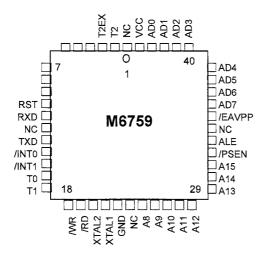

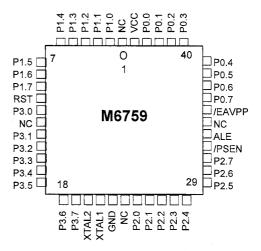

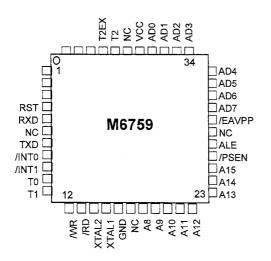

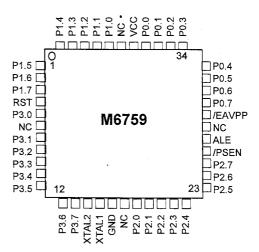

#### 44-pin PLCC Package

44-pin QFP Package

# 2.2 Pin Description Table

Pin assignments shown below are listed based on 44-pin PLCC package. And if not additionally specified, further pin number reference throughout this datasheet is, by default, referred to 44-pin PLCC package. As for the QFP package, the pin number assignment should be shifted accordingly, as comparatively shown in Section 2.1 Pinout Diagram.

| Pin Name                    | No. (PLCC)                   | Туре      | Description                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------------------|------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDD                         | 44                           | IN        | Power supply for internal operation, 5V input.                                                                                                                                                                                                                                                                           |  |  |

| GND                         | 22                           | IN        | Ground.                                                                                                                                                                                                                                                                                                                  |  |  |

|                             |                              |           | Port 0 is 8 bits bi-directional I/O port with internal pull high.                                                                                                                                                                                                                                                        |  |  |

| P0.7-P0.0<br>AD7-0          | 36,37,38,39,<br>40,41,42, 43 | I/O       | Multiplexed address/data bus. During the time when ALE is high, the LSB of a memory address is presented. When ALE falls, the port transitions to a bi-directional data bus. This bus is used to read external ROM and read/write external RAM memory or peripherals.                                                    |  |  |

| RST                         | 10                           | IN        | Reset signal of internal circuit, it must be kept 4 clocks to ensure being recognized by internal circuit. This signal will not affect internal SRAM.                                                                                                                                                                    |  |  |

| XTAL1                       | 21                           | IN        | Crystal In, can be used as external clock input.                                                                                                                                                                                                                                                                         |  |  |

| XTAL2                       | 20                           | OUT       | Crystal out, feedback of XTAL1.                                                                                                                                                                                                                                                                                          |  |  |

| /PSEN                       | 32                           | OUT       | Program Store Enable Output, commonly connected to external ROM memory as a chip enable during fetching and MOVC operation. /PSEN goes high during a reset condition.                                                                                                                                                    |  |  |

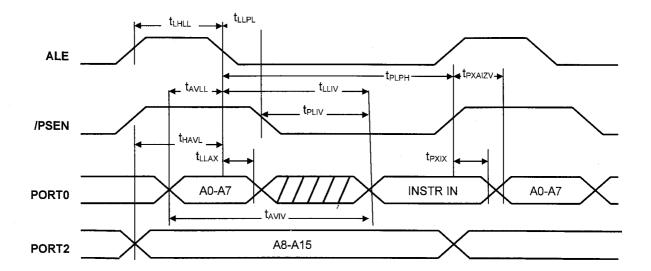

| ALE                         | 33                           | OUT       | Address Latch Enable, used to latch external LSB 8 bit address bus from multiplexed address/data bus, commonly connect to the latch enable of 373 family. This signal will be forced high when the device is in a reset condition.                                                                                       |  |  |

| P1.7-P1.0<br>T2EX<br>(P1.1) | 9,8,7,6,5,4,3                | I/O<br>IN | Port 1 is 8 bits bi-directional I/O port with internal pull high. All pins have an alternate function shown as below.  External timer/counter 2 trigger.                                                                                                                                                                 |  |  |

| T2 (P1.0)                   | ,2                           | IN        | External timer/counter 2.                                                                                                                                                                                                                                                                                                |  |  |

|                             |                              | I/O       | Port 2 is 8 bits bi-directional I/O port with internal pull high. The alternate function is MSB 8 bit address bus                                                                                                                                                                                                        |  |  |

| P2.7-P2.0<br>A15-A8         | 31,30,29,28,<br>27,26,25, 24 | OUT       | This bus emits the high-order address byte during fetches from external Program Memory or during accesses to external Data Memory that use 16-bit addresses (MOVX @ DPTR).  During accesses to external Data Memory that use 8-bit addresses (MOVX @ Ri), Port 2 emits the contents of the P2 Special Function Register. |  |  |

Model No.: LCT-17HT

| P3.7-P3.0  |                              | I/O | Port 3 is an 8-bit bi-directional I/O port with internal pull high. The |  |  |

|------------|------------------------------|-----|-------------------------------------------------------------------------|--|--|

| /RD (P3.7) | D (P3.7)                     |     | reset condition of this port is with all bits at a logic 1.             |  |  |

| /WR (P3.6) | 19,18,17,16,<br>15,14,13, 11 |     | Port 3 also have alternate function list below                          |  |  |

| T1 (P3.5)  |                              | OUT | External data memory read strobe.                                       |  |  |

| T0 (P3.4)  |                              | OUT | External data memory write strobe.                                      |  |  |

| /INT1      |                              | IN  | External timer/counter 1.                                               |  |  |

| (P3.3)     |                              | IN  | External timer/counter 0.                                               |  |  |

| /INT0      |                              | IN  | External interrupt 1 (Negative Edge Detect).                            |  |  |

| (P3.2)     |                              | IN  | External interrupt 0 (Negative Edge Detect).                            |  |  |

| TXD (P3.1) |                              | OUT | Serial port output.                                                     |  |  |

| RXD (P3.0) |                              | IN  | Serial port input.                                                      |  |  |

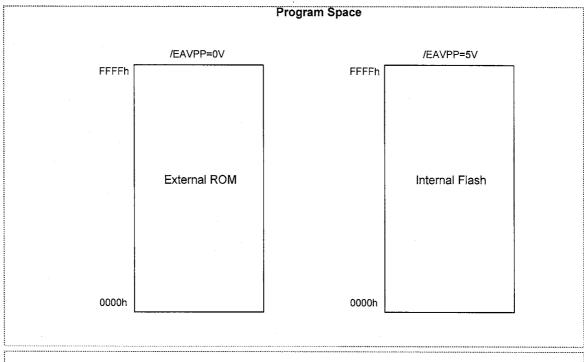

| /EAVPP     | 35                           | IN  | The pin must be externally held low to enable the device to fetch code  |  |  |

|            |                              |     | from external program memory. If /EAVPP is held high, the device        |  |  |

|            |                              |     | executes from internal program memory. /EAVPP is internal latched       |  |  |

|            |                              |     | on reset. This pin also receives the 12V programming voltage $(V_{PP})$ |  |  |

|            |                              |     | during FLASH programming.                                               |  |  |

| NC         | 1,12,23,34                   | NC  | These pins should not be connected for any purpose                      |  |  |

#### 3.0 FUNCTION DESCRIPTION

#### 3.1 Data Space Addressing

The M6759 has internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes Special Function Register (SFR), and 256 bytes auxiliary RAM (ARAM).

The four segments are:

- a. The Lower 128 bytes of RAM (address 00H to 7FH) are directly and indirectly addressable.

- b. The Upper 128 bytes of RAM (address 80H to FFH) are indirectly addressable only.

- c. The Special Function Registers SFRs, (address 80H to FFH) are directly addressable only.

- d. The 256-bytes auxiliary RAM (ARAM, 0000H-00FFH) are indirectly accessed by move external instruction, MOVX.

Either direct or indirect addressing can access the lower 128 bytes. The upper 128 bytes can be accessed by indirect address only. The upper 128 bytes occupy the same address space as the SFRs. That means they have the same address, but are physically separate from SFR space.

The ARAM can be accessed by indirect addressing and MOVX instructions when ARAM\_EN bit is set. This part of memory is physically located on-chip, logically occupied the first 256-bytes of external data memory if ARAM EN bit is set.

The ARAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to ARAM will not affect ports P0, P3.6 (/WR) and P3.7 /RD).

If ARAM\_EN is cleared, the access to external memory will be performed in the same way as standard 8051. If ARAM\_EN is set and DPTR contains value lower than 0100H, the ARAM will be accessed rather than external memory, but if DPTR contains value higher than 00FFH (i.e. 0100H to FFFFH), the external memory will be accessed.

If ARAM\_EN is set and P2 SFR contains 00H, the ARAM will be accessed by the MOVX @Ri, #data instruction, but if P2 SFR contains a non-zero value, the external memory will be accessed using MOVX @Ri, #data.

For example,

MOVX DPTR, #data

If ARAM\_EN is set and DPTR contains 0030H, access the ARAM at address 030H rather than external memory.

If ARAM EN is set and DPTR contains 0130H, the external memory address 0130H will be accessed

Model No.: LCT-17HT

For example:

MOVX

@R0, #data

If ARAM\_EN is set, P2 SFR contains 00H, and R0 contains 30H, an access to the ARAM at address 30H will be performed.

If ARAM\_EN is set, P2 SFR contains 01H, and R0 contains 30H, an access to the external memory address 0130H will be performed if P2 is connected to the high byte address bus of external RAM.

#### 3.2 Dual Data Pointer

Data memory block moves can be accelerated using the Dual Data Pointer (DPTR). The standard 8051 DPTR is a 16-bit value that is used to address off-chip data RAM or peripherals. In the M6759, the standard 16-bit data pointer is called DPTR0 and is located at SFR address 82H and 83H. These are the standard locations. The new DPTR is located at SFR 84H and 85H and is called DPTR1. The new DPTR Select bit (DPS) chooses the active pointer and is located at the LSB of the SFR location 86H. No other bits in register 86H have any effect and are set to 0. The user switches between data pointer by toggling the LSB of register 86H. The increment (INC) instruction is the fastest way to accomplish this. All DPTR-related instructions use the currently selected DPTR for any activity.

#### 3.3 Low EMI Mode

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purpose. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

If desired, setting bit 0 of SFR location 8EH can disable ALE operation. With the bit set, ALE is active only during a MOVX instruction. Otherwise the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the micro-controller is in external execution mode.

Model No.: LCT-17HT

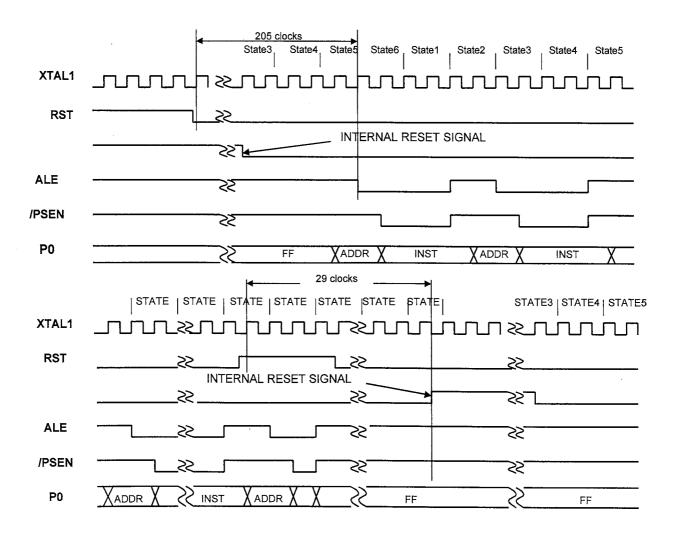

# **Memory Map**

Model No.: LCT-17HT

#### 3.4 Idle Mode

In Idle mode, CPU put itself into sleep while all the on-chip peripherals remain active. The instruction that sets PCON.0 is the last instruction executed in the normal operating mode before Idle mode is activated. The content of RAM and special functions register remain unchanged, and the status of CPU (includes Stack Point, Program Counter, Program Status Word and Accumulator) is preserved in this mode.

There are two ways to terminate Idle mode:

- Activation of any enabled interrupt will cause IDLE (PCON.0) to be cleared by hardware terminating Idle mode. The interrupt will be serviced, and returned by instruction RETI. The next instruction to be executed is the one which follows the instruction that wrote a logic 1 to PCON.0. The flag bits GF0 (PCON.2) and GF3 (PCON.6) can be used to determine whether the interrupt was received during normal execution or during the Idle mode. When Idle mode is terminated by an interrupt, the service routine can examine the status of the flag bits.

- > The second way of terminating the Idle mode is with an external hardware reset.

#### 3.5 Power Down Mode

Setting PCON.1 (PD) can force CPU enter Power Down mode. In this mode, on-chip oscillator is stopped to save most of power. All functions are stopped due to the clock frozen, but the contents of RAM and special functions register are held.

To terminate Power Down mode, the only way is hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart stably.

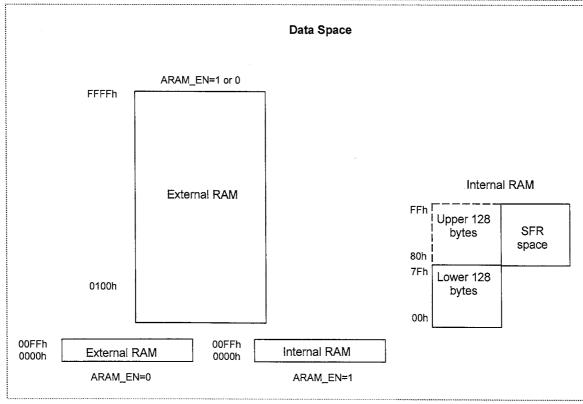

#### 3.6 Reset

The RST is the reset input, which is the input to a Schmitt Trigger. A reset is accomplished by holding the RST pin high for at least four oscillator periods while the oscillator is running. The CPU responds by generating an internal reset, with the timing shown in Reset Timing. The external reset signal is synchronous to the internal clock. The port pins will maintain high by internal pull-ups for 205 oscillator periods after RST pin goes low. While the RST pin is high, ALE and /PSEN are weakly pulled high. After RST is pulled low, it will take about 205 oscillator periods for ALE and PSEN to start clocking. For this reason, other devices can not be synchronized to the internal timings of the m6759. Driving the ALE and /PSEN pins to 0 while reset is active could cause the device to go into an indeterminate state.

The internal reset algorithm writes 0s to all the SFRs except the port latches, the Stack Pointer, and SBUF. The port latches are initialized to FFH, the Stack Pointer to 07H, and SBUF is indeterminate. The internal RAM is not affected by reset. On power up the RAM content is indeterminate.

Model No.: LCT-17HT

#### 3.7 Interrupt Processing

When an enabled interrupt occurs, the CPU vectors to the address of the interrupt service routine (ISR) associated with that interrupt, as listed in Table 11. The CPU executes the ISR to completion unless another interrupt of higher priority occurs. Each ISR ends with a RETI (return from interrupt) instruction. After executing the RETI, the CPU returns to the next instruction that would have been executed if the interrupt had not occurred.

An ISR can only be interrupted by a higher priority interrupt. That is, an ISR for a low-priority level interrupt can only be interrupted by high-priority level interrupt. An ISR for a high-priority level cannot be interrupted by any other interrupt.

M6759 always completes the instruction in progress before servicing an interrupt. If the instruction in progress is RETI, or a write access to any of the IP or IE SFRs, M6759 completes one additional instruction before servicing the interrupt.

#### 3.8 Interrupt Masking

The EA bit in the IE SFR (IE.7) is a global enable for all interrupts. When EA=1, each interrupt is enabled/masked by its individual enable bit. When EA=0, all interrupts are masked.

#### 3.9 Interrupt Priorities

There are two stages of interrupt priority assignment, interrupt level and natural priority. The interrupt level (high or low) takes precedence over natural priority. All interrupts can be assigned to be high or low priority. In addition to an assigned priority level, each interrupt also has a natural priority, as listed in Table 3-2. Simultaneous interrupts with the same priority level (for example, both high) are resolved according to their natural priority. For example, if /INT0 and /INT1 are both programmed as high priority, /INT0 takes precedence.

Once an interrupt is being serviced, only an interrupt of higher priority level can interrupt the service routine of the interrupt currently being serviced.

| Mode       | Program  | ALE | /PSEN | Port0 | Port1 | Port2   | Port3 |

|------------|----------|-----|-------|-------|-------|---------|-------|

|            | Memory   |     |       |       |       |         |       |

| Idle       | Internal | 1   | 1     | Data  | Data  | Data    | Data  |

| Idle       | External | 1   | 1     | Float | Data  | Address | Data  |

| Power Down | Internal | 0   | 0     | Data  | Data  | Data    | Data  |

| Power Down | External | 0   | 0     | Float | Data  | Data    | Data  |

Table 3-1. Status of the External pins During Idle and Power Down

Model No.: LCT-17HT

# **Reset Timing**

**Table 3-2. Interrupt Natural Vectors and Priorities**

| Interrupt | Description                               | Natural Priority | Interrupt Vector |

|-----------|-------------------------------------------|------------------|------------------|

| /INT0     | External interrupt 0                      | 0                | 03H              |

| TF0       | Timer 0 interrupt                         | 1                | 0BH              |

| /INT1     | External interrupt 1                      | 2                | 13H              |

| TF1       | Timer 1 interrupt                         | 3                | 1BH              |

| TI or RI  | Serial Port transmit or receive interrupt | 4                | 23H              |

| TF2       | Timer 2 interrupt                         | 5                | 2BH              |

Table 3-3. Interrupt Flag, Enables and Priority Control

| Interrupt | Description                               | Flag    | Enable | <b>Priority Control</b> |  |

|-----------|-------------------------------------------|---------|--------|-------------------------|--|

| /INT0     | External interrupt 0                      | TCON.1  | IE.0   | IP.0                    |  |

| TF0       | Timer 0 interrupt                         | TCON.5  | IE.1   | IP.1                    |  |

| /INT1     | External interrupt 1                      | TCON.3  | IE.2   | IP.2                    |  |

| TF1       | Timer 1 interrupt                         | TCON.7  | IE.3   | IP.3                    |  |

| TI or RI  | Serial Port transmit or receive interrupt | SCON0.0 | IE.5   | IP.5                    |  |

| HOIRI     | Senai Port transmit of receive interrupt  | SCON0.1 |        | 16.5                    |  |

| TF2       | Timer 2 interrupt                         | T2CON.7 | IE.6   | IP.6                    |  |

Model No.: LCT-17HT

# 4.0 SPECIAL FUNCTION REGISTERS

# SFR Register Map

| Register | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Addr |

|----------|---------|-------|-------|-------|-------|-------|--------|--------|------|

| P0       |         |       |       |       |       |       |        |        | 80H  |

| SP       |         |       |       |       |       |       |        |        | 81H  |

| DPL0     |         |       |       |       |       |       |        |        | 82H  |

| DPH0     |         |       |       |       |       |       |        |        | 83H  |

| DPL1     |         |       |       |       |       |       |        |        | 84H  |

| DPH1     |         |       |       |       |       |       |        |        | 85H  |

| DPS      | 0       | 0     | 0     | 0     | 0     | 0     | 0      | SEL    | 86H  |

| PCON     | SMOD    | GF4   | GF3   | GF2   | GF1   | GF0   | STOP   | IDLE   | 87H  |

| TCON     | TF1     | TR1   | TF0   | TR0   | IE1   | IT1   | IE0    | IT0    | 88H  |

| TMOD     | GATE    | C/T   | M1    | M0    | GATE  | C/T   | M1     | M0     | 89H  |

| TL0      |         |       |       |       |       |       |        |        | 8AH  |

| TL1      |         |       |       |       |       |       |        |        | 8BH  |

| TH0      |         |       |       |       |       |       |        |        | 8CH  |

| TH1      |         |       |       |       |       |       |        |        | 8DH  |

| LEMI     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | LOWEMI | 8EH  |

| P1       |         |       |       |       |       |       |        |        | 90H  |

| AUXR     | ARAM_EN | GF6   | GF5   | *EB   | *BRG1 | *BRG0 | *INT2I | *INT2E | 97H  |

| SCON     | SM0     | SM1   | SM2   | REN   | TB8   | RB8   | TI     | RI     | 98H  |

| SBUF     |         |       |       |       |       |       |        |        | 99H  |

| P2       |         |       |       |       |       |       |        |        | A0H  |

| IE       | EA      | *EX2  | ET2   | ES0   | ET1   | EX1   | ET0    | EX0    | A8H  |

| Р3       |         |       |       |       |       |       |        |        | ВОН  |

| IP       | 1       | *PX2  | PT2   | PS0   | PT1   | PX1   | PT0    | PX0    | B8H  |

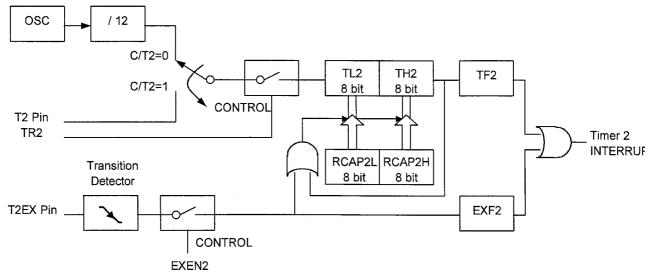

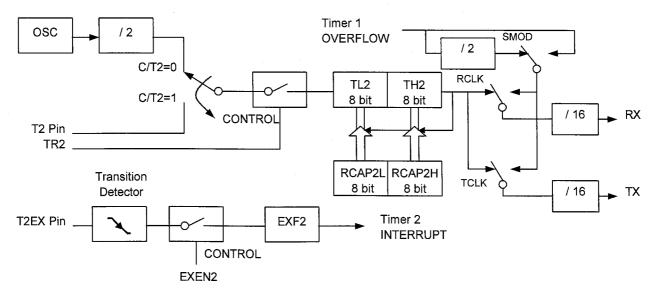

| T2CON    | TF2     | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | C/T2   | CP/RL2 | C8H  |

| RCAP2L   |         |       |       |       |       |       |        |        | CAH  |

| RCAP2H   |         |       |       |       |       |       |        |        | СВН  |

| TL2      |         |       |       |       |       |       |        |        | ССН  |

| TH2      |         |       |       |       |       |       |        |        | CDH  |

| PSW      | CY      | AC    | F0    | RS1   | RS0   | OV    | F1     | P      | D0H  |

| ACC      |         |       |       |       |       |       |        |        | Е0Н  |

| *P4      |         |       |       |       |       |       |        |        | E8H  |

| В        |         |       |       |       |       |       |        |        | F0H  |

| *P5      |         |       |       |       |       |       |        |        | F8H  |

All register labeled with \* can be only used in 68-pin package (not available now)

Model No.: LCT-17HT

# SFR Register Initial Value

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Addr |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| P0       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 80H  |

| SP       | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 81H  |

| DPL0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 82H  |

| DPH0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 83H  |

| DPL1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 84H  |

| DPH1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 85H  |

| DPS      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 86H  |

| PCON     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 87H  |

| TCON     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 88H  |

| TMOD     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 89H  |

| TL0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 8AH  |

| TL1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 8BH  |

| TH0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 8CH  |

| TH1      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 8DH  |

| LEMI     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 8EH  |

| P1       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 90H  |

| AUXR     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 97H  |

| SCON     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 98H  |

| SBUF     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 99H  |

| P2       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | A0H  |

| ΙE       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | A8H  |

| P3       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | вон  |

| IP       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | B8H  |

| T2CON    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | C8H  |

| RCAP2L   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | CAH  |

| RCAP2H   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | СВН  |

| TL2      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | CCH  |

| TH2      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | CDH  |

| PSW      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | D0H  |

| ACC      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | E0H  |

| P4       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | E8H  |

| В        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | F0H  |

| P5       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | F8H  |

Model No.: LCT-17HT

# **Register Definition**

# 4.1 CPU Control and Status Register

SFR 86H: DPS register, Data Pointer Select Register

| Bit | Description                                                                                 |

|-----|---------------------------------------------------------------------------------------------|

| 7-1 | 0                                                                                           |

| 0   | SEL. The DPTR Select bit. When SEL=0, DPTR0 is the active pointer. When SEL=1, DPTR1 is the |

|     | active pointer.                                                                             |

# SFR 87H: PCON Register, Power Control Register

| Bit | Description                                                                                       |

|-----|---------------------------------------------------------------------------------------------------|

| 7   | SMOD, Double Baud Rate bit. If Timer 1 is used to generate baud rate and SMOD=1, the baud rate is |

|     | doubled when the Serial Port is used in modes 1, 2 or 3.                                          |

| 6-2 | GF3–GF0, General Purpose Flag bit.                                                                |

| 1   | PD, Power Down bit.                                                                               |

| 0   | IDLE, Idle Mode bit.                                                                              |