# SERVICE MANUAL

# TF1560GH C383 S383FA-V151

#### 5. CIRCUIT-DESCRIPTION

# 5-1 THE DIFFERENT between LG-Panel & Samsung-Panel & CPT-Panel & Hannstar- Panel in ELECTRICAL Charateristic

| <u>LG-Panel</u>          | <ol> <li>Two CCFL (Cold Cathode Fluorescent Tube)</li> <li>Single Pixel, 6 bit color (262144 colors)</li> <li>Panel Vdd = 3.3V (in JP202 select 3.3V)</li> </ol> |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Samsung-Panel 1. Four CC | CFL (Cold Cathode Fluorescent Tube)                                                                                                                              |

|                          | 2. Double Pixel, 6 bit color (262144 colors)                                                                                                                     |

|                          | 3. Panel Vdd = $5V$ (in JP201 select $5V$ )                                                                                                                      |

| Chung-Hwa Panel          | 1. Two CCFL (Cold Cathode Flourescent Tube)                                                                                                                      |

| -                        | 2. Double Pixel, 8 bit color (16.7 Million colors)                                                                                                               |

|                          | 3. Panel Vdd = $5V$ (in JP201 select $5V$ )                                                                                                                      |

| Hannstar Panel 1. Two CC | CFL (Cold Cathode Flourescent Tube)                                                                                                                              |

|                          | 2. Double Pixel, 6 bit color (262144 colors)                                                                                                                     |

|                          | 3. Panel Vdd = $3.3V$ (in JP202 select $3.3V$ )                                                                                                                  |

#### 5-2 SPECIAL FUNCTION with PRESS-KEY

press ENTER-key 2 seconds, at POWER-ON: set to FACTORY-mode, when we want to adjust white-balance with rs232-port or view Power-on-timer. In this mode, OSDscreen will locate in left top of screen.

Press POWER-key off-on : CANCEL above function(quit from factory mode) and set to user-mode. Press both Left & Right key and switching on-off key : Enable/ Disable OSD-LOCK function

#### **OSD-INDEX EXPLANATION**

- 1. CABLE NOT CONNECTED : Signal-cable not connected.

- 2. INPUT NOT SUPPORT :

a. INPUT frequency out of range : H > 62kHz, v > 75Hz or H < 28kHz, v < 55Hz

b. INPUT frequency out of VESA-spec. (out of tolerance too far)

3. UNSUPPORT mode, try different Video-card Setting : Input frequency out of tolerance, but still can catch-up by our system (if this message show, that means, this is new-user mode, AUTO-CONFIG will disable)

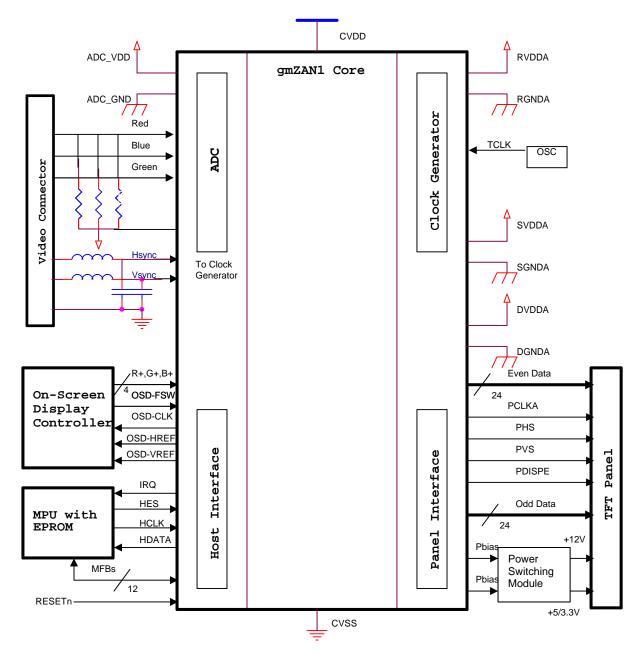

#### 5-3 SIMPLE-INTRODUCTION about LM500 chipset

- GMZAN1 (Genesis all-in-one solution for ADC, OSD, scalar and interpolation): USE for computer graphics images to convert analog RGB data to digital data for interpolation process, zooming, OSD font & overlay and generate drive-timing for LCD-PANEL,

- M6759 (ALI- MCU, type 8052 series with 64k Rom-size and 512 byte ram): Use for calculate frequency, pixel-dot, detect change mode, rs232-communication, power-consumption control, OSD-index warning...etc.

- 3. 24LC21 (MicroChip IC) : EePROM type, 1K ROM-SIZE, for saving DDC-CONTENT.

- 4. 24C04 (ATMEL IC) :

EePROM type, 4K ROM-SIZE, for saving AUTO-config data, White-balance data, and Power-key status and power on -counter data.

- 5. LM2569S( NS brand swintching regulator 12V to 5V with 3A load current) :

- 6. AIC 1084-33CM (AIC brand linear regulator 5V to 3.3V)

#### MODULE-TPYE COMPONENT :

- 1. ADAPTER : CONVERSION-module to convert AC 110V-240V to 12VDC, with 3.5 AMP

- 2. INVERTER : CONVERSION-module to convert DC 12V to High-Voltage around 1600V, with frequency 30K-50Khz, 7mA-9mA

#### 6. Trouble-Shooting

\*\*Use the PC Win 98/95 white pattern, with some icon on it, and Change the Resolution to 640x480 60 Hz / 31 KHz

**\*\*NOTICE :** This system free-running freq. is 48 KHz / 60 Hz, so you better use another frequency to do trouble shooting(ex:31kHz 60Hz) this trouble shooting is proceed with 640x480 @60Hz 31Khz

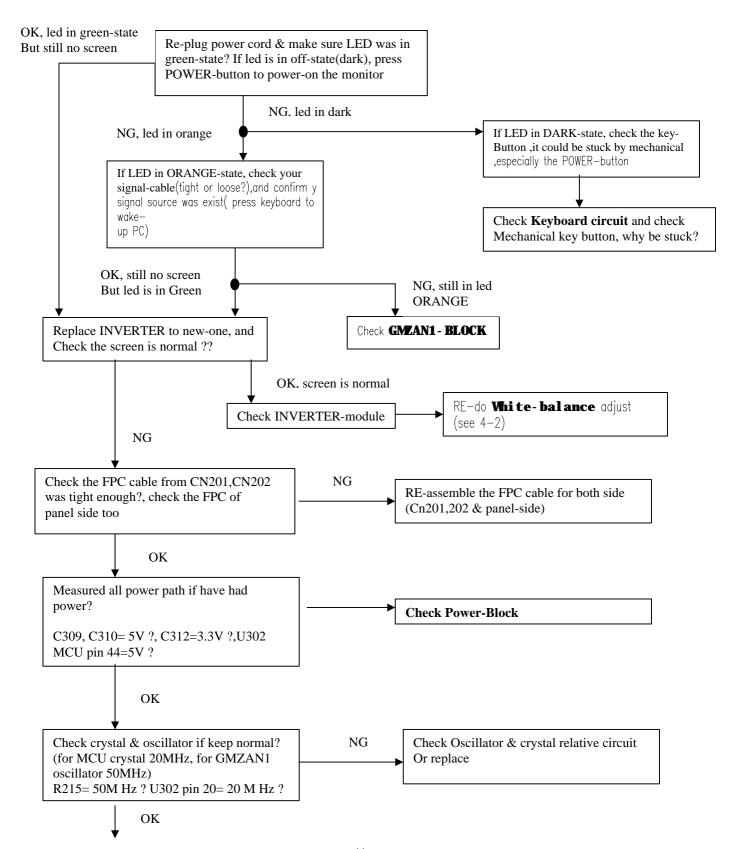

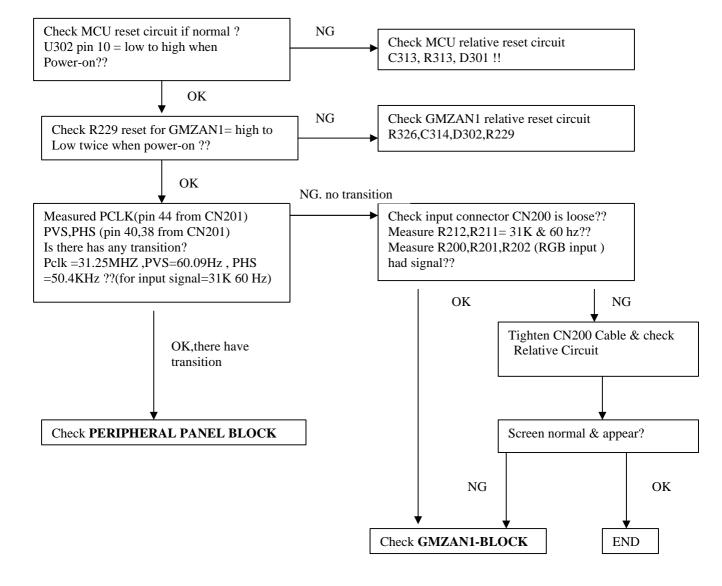

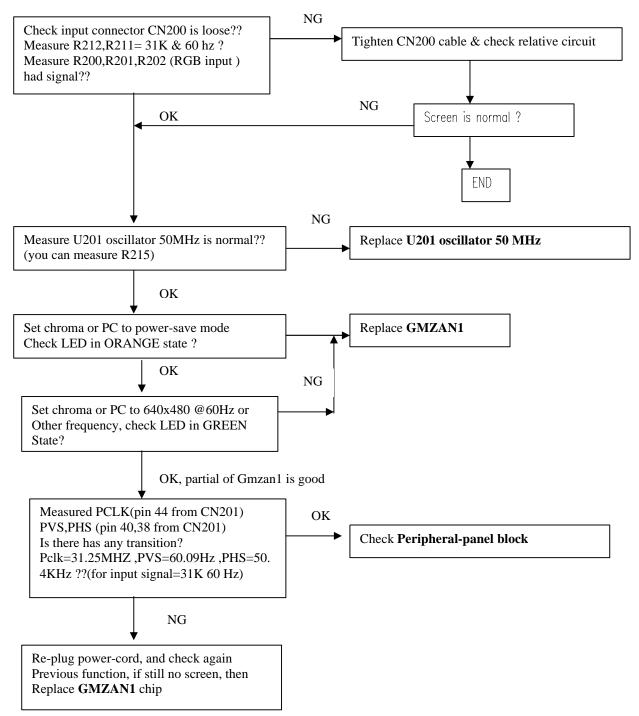

### I. NO SCREEN APPEAR

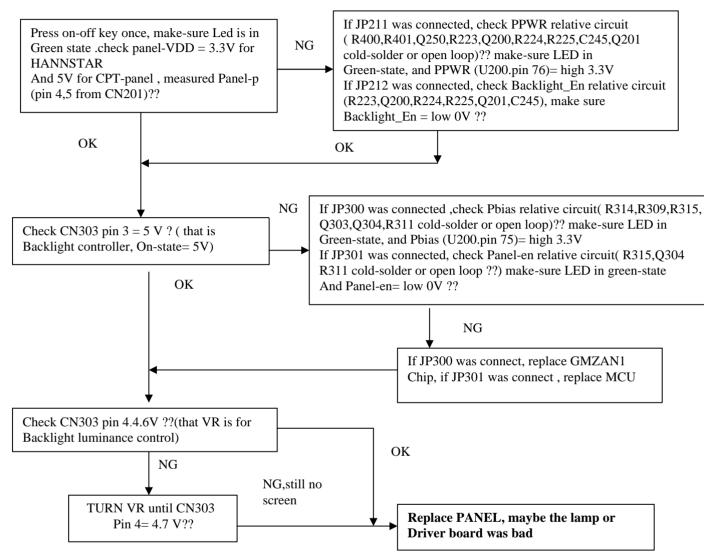

#### PERIPHERAL PANEL BLOCK

Note: "Panel vdd " and "backlight on-off " can be direct control by :

GMZAN1 or MCU

Some panel can direct control by GMZAN1 ,if the relative timing between panel-vdd and backlight on-off is short (under 80 ms), otherwise, will be control by MCU

If J211 be connected, that means Panel-VDD control was by GMZAN1 ,otherwise by MCU(JP212)

If J300 be connected, that means Backlight control was by GMZAN1 ,otherwise by MCU (JP301)

BUT Hannstar panel & CPT panel still control by J211 & J300

FOR HANNSTAR-PANEL, there is the relative timing between input resolution to output timing for panel (output timing from GMZAN1 chip) as follow :

| RESOLUTION( from PC or chroma) | PCLK(U200.44 | 4) PHS ( U200 | .74) PVS (U200.73) |

|--------------------------------|--------------|---------------|--------------------|

| 640X480 @60 Hz                 | 31.25MHz     | 50.4 KHz      | 60.09 Hz           |

| 640X480 @70 Hz                 | 35.56MHz     | 55.93KHz      | 69.83 Hz           |

| 640X480 @72 Hz                 | 36.76MHz     | 57.64KHz      | 71.94 Hz           |

| 640X480 @75 Hz                 | 37.71MHz     | 60.12KHz      | 74.96 Hz           |

| 800X600 @60 Hz                 | 28.65MHz     | 48.45KHz      | 60.39 Hz           |

| 800X600 @70 Hz                 | 32.94MHz     | 56.05KHz      | 70.03 Hz           |

| 800X600 @72 Hz                 | 34.25MHz     | 57.61KHz      | 72.04 Hz           |

| 800X600 @75 Hz                 | 35.71MHz     | 60.10KHz      | 75.08 Hz           |

| 1024x768@60 Hz                 | 28.57MHz     | 48.36KHz      | 60.09 Hz           |

| 1024x768@70 Hz                 | 32.77MHz     | 56.05KHz      | 70.03 Hz           |

| 1024x768 @72 Hz                | 33.97MHz     | 57.60KHz      | 71.84 Hz           |

| 1024x768@75 Hz                 | 35.41MHz     | 60.24KHz      | 74.96 Hz           |

#### **GMZAN1 BLOCK check**

Note : set the input signal ( PC or CHROMA) to 640x480 31k 60 hz

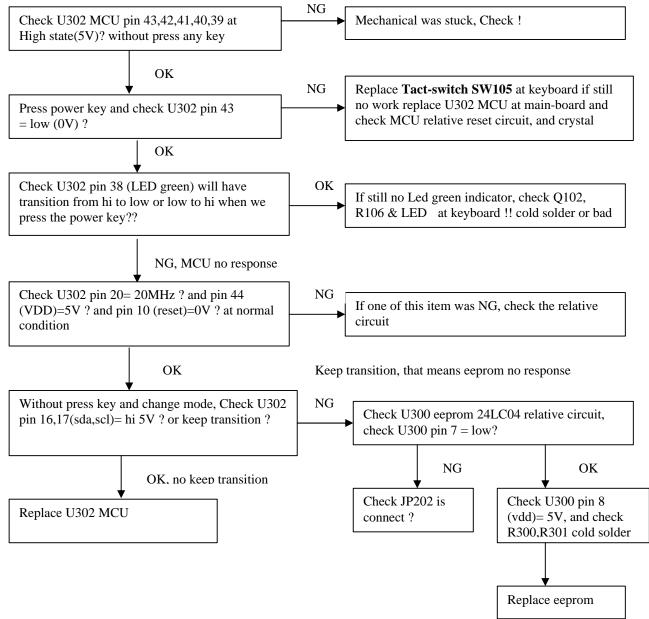

# **KEYBOARD BLOCK check**

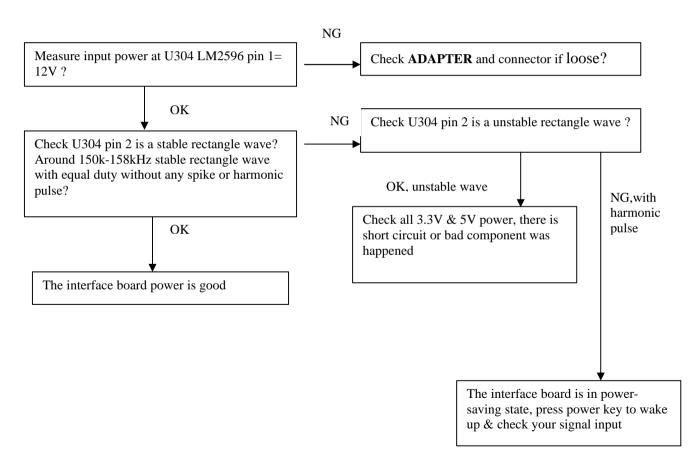

# **POWER-BLOCK** check

\*\*Note : the waving of U304 pin 2 can determined the power situation

- 1. stable rectangle wave with equal duty, freq around 150K-158KHz that means all power of this interface board is in normal operation ,all status of 5V & 3.3V is normal working

- 2. unstable rectangle wave without same duty, that means ABNORMAL operation was happened check 3.3V or 5V ,short-circuit or bad component

- 3. rectangle wave with large spike & harmonic pulse on front side of rectangle wave, that means all 3.3v is no load, **Gmzan1** was shut-down, and only **MCU** still working ,the monitor is in power saving state

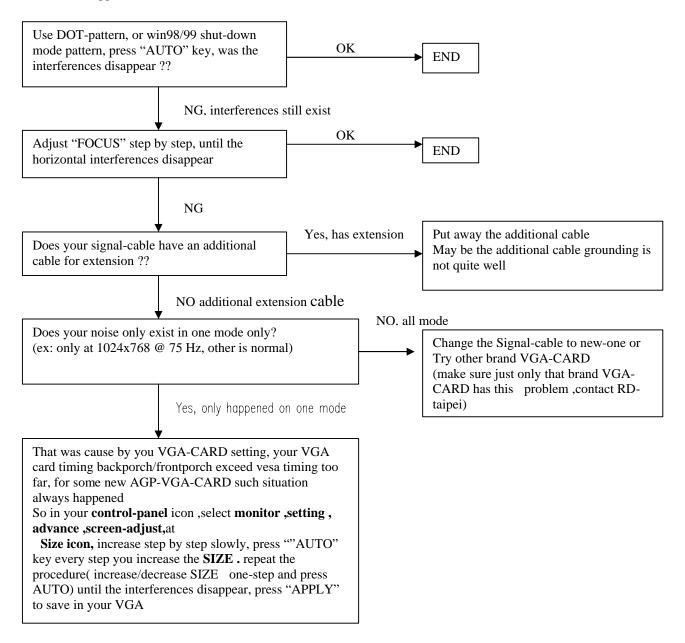

#### II.ALL SCREEN HAS INTERFERENCES OR NOISE, CAN'T BE FIXED BY AUTO KEY

**\*\* NOTE:** There is so many kind of interferences, 1). One is cause by some VGA-CARD that not meet VESA spec or power grounding too bad that influence our circuit

2).other is cause by external interferences, move the monitor far from electronic equipment.( rarely happened)

# III. DOS MODE has jitter

NOTE :the rule of doing AUTO-CONFIGURATION : must be a full-size screen, if the screen not full , the autoconfiguration will fail. So in dos mode ,just set your "CLOCK" in OSD-MENU to zero or use some full screen edit file (ex: PE2, HE) and press "AUTO"

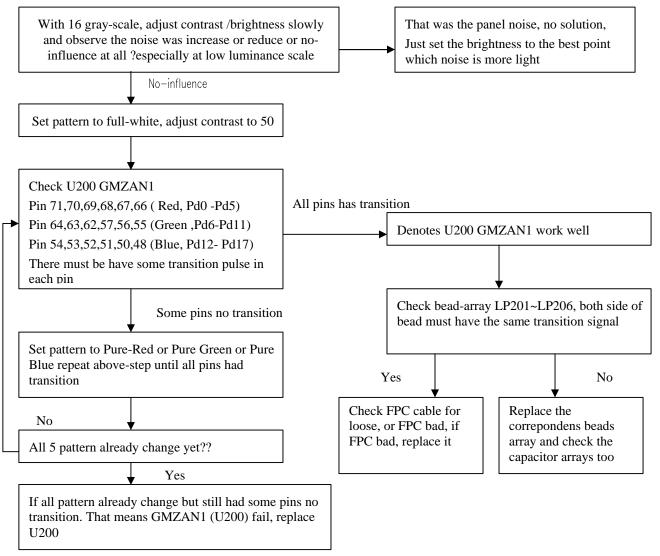

#### **I?**. THERE WAS SNOW PHENOMENA or BRIGHT NOISE ON THE SCREEN

When use pattern 32 Gray-scale / or 16 Gray scale, there is a **snow phenomena on the screen (like a noise spread** inside) that means some output bit to panel was bad, may be cause by FPC loose, or bead-array cold-solder

There were some panel (ex :LG), also have this phenomena too, the noise will reduce or increase depend on the contrast/brightness value, this kind of problem was cause by Panel-driver-board it self, we can't fix it , the only way to do was find the best-point of brightness/contrast, that the noise is more light

| Use following pattern : |                        |                                             |

|-------------------------|------------------------|---------------------------------------------|

| 1. pure-white           | 2. Pure Red            | 3. Pure Green                               |

| 4. Pure Blue            | 5. Pure White          | 6. Character                                |

| repeat measure GMZAN1   | (U200) all output pins | must have some transition pulse, but notice |

- 1. For LG panel and HANNSTAR panel , only 6 bit has output, (PD0~ PD17 , PD36 ~ PD41) the corresponding beads was LP201 ~ LP206

- **2.** For Chung-hwa panel or other's 8 bit panel, all output are available (PD0-PD47 ), the corresponding beads was LP201-LP212

#### **Ex : HANNSTAR Panel 6 bits**

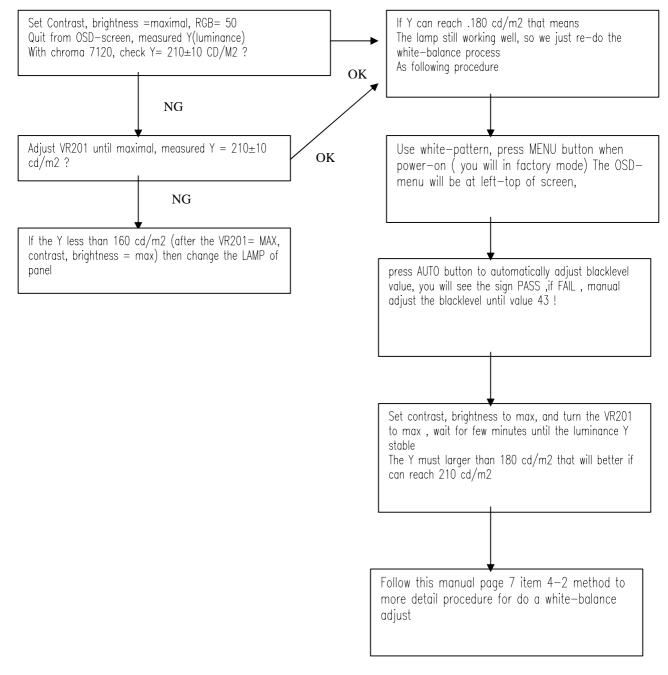

# **V.** THE PANEL LUMINANCE WAS DOWN

#### GMZAN1

The gmZAN1device utilizes Genesis' patented third-generation Advanced Image Magnification technology as well as a proven integrated ADC/PLL to provide excellent image quality within a cost effective SVGA/XGA LCD monitor solution.

As a pin-compatible replacement for the gmB120, the gmZAN1 incorporates all of the gmB120 features plus many enhanced features; including 10-bit gamma correction, Adaptive Contrast Enhancement (ACE) filtering, Sync On Green (SOG), and an enhanced OSD.

#### **1.1 Features**

- Solution Fully integrated 135MHz 8-bit triple-ADC, PLL, and pre-amplifier

- Section 2 Scaling algorithm featuring new Adaptive Contrast Enhancement (ACE)

- Solution Con-chip programmable OSD engine

- 10-bit programmable gamma correction

- Most interface with 1 or 4 data bits

- ∠ Pin-compatible with gmB120

#### **Integrated Analog Front End**

- ∠ Integrated 8-bit triple ADC

- ∠ Up to 135MHz sampling rates

- No additional components needed

- All color depths up to 24-bits/pixel are supported

### **High-Quality Advanced Scaling**

- ∠ Fully programmable zoom

- M Independent horizontal / vertical zoom

- Enhanced and adaptive scaling algorithm for optimal image quality

- Recovery Mode / Native Mode

#### **Input Format**

- Analog RGB up to XGA 85Hz

- Support for Sync On Green (SOG)

- Support for composite sync modes

#### **Output Format**

- Support for 8 or 6-bit panels (with high quality dithering)

- Solution One or two pixel output format

#### **Built In High-Speed Clock Generator**

- Sc Fully programmable timing parameters

- Solution Solution Constrained and presence of the contract of

#### Auto-Configuration / Auto-Detection

- Phase and image positioning

- ∠ Input format detection

#### **Operation Modes**

- Bypass mode with no filtering

- Multiple zoom modes:

- ∠ With filtering

- & With adaptive (ACE) filtering

#### **Integrated On-Screen Display**

- $\mathscr{A}$  On-chip character RAM and ROM for better customization

- External OSD supported for greater flexibility

- Supports both landscape and portrait fonts

- Many other font capabilities including: blinking, overlay and transparency

#### **1.3 Pin Description**

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

| PIN # | Name      | I/O | Description                                                                                               |

|-------|-----------|-----|-----------------------------------------------------------------------------------------------------------|

| 77    | ADC_VDD2  |     | Digital power for ADC encoding logic. Must be bypassed with 0.1uF capacitor to                            |

|       |           |     | pin 78 (ADC_GND2)                                                                                         |

| 78    | ADC_GND2  |     | Digital GND for ADC encoding logic. Must be directly connected to the digital                             |

|       |           |     | system ground plane.                                                                                      |

| 79    | ADC_VDD1  |     | Digital power for ADC clocking circuit. Must by passed with 0.1uF capacitor to pin 80 (ACD_GND1).         |

|       |           |     | Digital GND for ADC clocking circuit. Must be directly connected to the digital                           |

| 80    | ADC_GND1  |     | system ground plane.                                                                                      |

| 81    | SUB_GNDA  |     | Dedicated pin for substrate guard ring that protects the ADC reference system.                            |

| 01    | SOD_ONDA  |     | Must be directly connected to the analog system ground plane.                                             |

| 82    | ADC_GNDA  |     | Analog ground for ADC analog blocks that are shared by all three channels.                                |

|       | —         |     | Includes bandgap reference, master biasing and full scale adjust. Must be directly                        |

|       |           |     | connected to analog system ground plane.                                                                  |

| 84    | ADC_VDDA  |     | Analog power for ADC analog blocks that are shared by all three channels.                                 |

|       |           |     | Includes bandgap reference, master biasing and full scale adjust. Must be                                 |

|       |           |     | bypassed with 0.1uF capacitor to pin 82 (ADC_GNDA).<br>For internal testing purpose only. Do not connect. |

| 83    | Reserved  |     |                                                                                                           |

| 85    | ADC_BGNDA |     | Analog ground for the blue channel. Must be directly connected to the analog                              |

|       |           |     | system ground plane.                                                                                      |

| 88    | ADC_BVDDA |     | Analog power for the blue channel. Must be bypassed with 0.1uF capacitor to pin 85(BGNDA).                |

| 86    | BLUE-     | Ι   | Negative analog input for the Blue channel.                                                               |

| 87    | BLUE+     | Ι   | Positive analog input for the Blue channel.                                                               |

| 89    | ADC_GGNDA |     | Analog ground for the green channel. Must be directly connected to the analog system ground plane.        |

| 92    | ADC_GVDDA |     | Analog power for the green channel. Must be bypassed with 0.1uF capacitor to pin 89 (ADC_GGNDA).          |

| 90    | GREEN-    | Ι   | Negative analog input for the Green channel.                                                              |

| 91    | GREEN+    | Ι   | Positive analog input for the Green channel.                                                              |

| 93    | ADC_RGNDA |     | Analog ground for the red channel. Must be directly connected to the analog system ground plane.          |

| 96    | ADC_RVDDA |     | Analog power for the red channel. Must be bypassed with 0.1uF capacitor to pin 93 (ADC_RGNDA).            |

| 94    | RED-      | Ι   | Negative analog input for the Red channel.                                                                |

| 95    | RED+      | Ι   | Positive analog input for the Red channel.                                                                |

Table 1 : Analog-to-Digital Converter

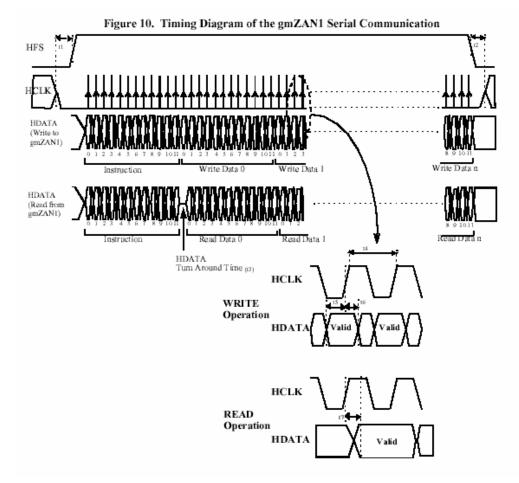

# Table 2 : Host Interface (HIF) / External On-Screen Display

| PIN # | Name      | I/O | Description                                                                                                                                                                                                                                                 |  |  |  |

|-------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 98    | HFS       | Ι   | Host Frame Sync. Frames the packet on the serial channel.                                                                                                                                                                                                   |  |  |  |

| 103   | HCLK      | Ι   | Clock signal input for the 3-wire serial communication.                                                                                                                                                                                                     |  |  |  |

| 99    | HDATA     | I/O | Data signal for the 3-wire serial communication.                                                                                                                                                                                                            |  |  |  |

| 100   | RESETn    | Ι   | Resets the gmZAN1 chip to a known state when low.                                                                                                                                                                                                           |  |  |  |

| 101   | IRQ       | 0   | Interrupt request output.                                                                                                                                                                                                                                   |  |  |  |

| 115   | OSD-HREF  | 0   | HSYNC output for an external OSD controller chip.                                                                                                                                                                                                           |  |  |  |

| 116   | OSD-VREF  | 0   | VSYNC output for an external OSD controller chip.                                                                                                                                                                                                           |  |  |  |

| 117   | OSD-Clk   | 0   | Clock output for an external OSD controller chip.                                                                                                                                                                                                           |  |  |  |

| 118   | OSD-Data0 | Ι   | Data input 0 from an external OSD controller chip.                                                                                                                                                                                                          |  |  |  |

| 119   | OSD-Data1 | Ι   | Data input 1 from an external OSD controller chip.                                                                                                                                                                                                          |  |  |  |

| 120   | OSD-Data2 | Ι   | Data input 2 from an external OSD controller chip.                                                                                                                                                                                                          |  |  |  |

| 121   | OSD-Data3 | Ι   | Data input 3 from an external OSD controller chip.                                                                                                                                                                                                          |  |  |  |

| 122   | OSD-FSW   | Ι   | External OSD window display enable. Displays data from external OSD controller when high.                                                                                                                                                                   |  |  |  |

| 123   | MFB11     | I/O | Multi-Function Bus 11. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                      |  |  |  |

| 124   | MFB10     | I/O | Multi-Function Bus 10. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                      |  |  |  |

| 102   | MFB9      | I/O | Multi-Function Bus 9. One of twelve multi-function signals MFB[11:0].<br>Also used as HDATA3 in a 4-bit host interface configuration.                                                                                                                       |  |  |  |

| 104   | MFB8      | I/O | Multi-Function Bus 8. One of twelve multi-function signals MFB[11:0].<br>Also used as HDATA2 in a 4-bit host interface configuration.                                                                                                                       |  |  |  |

| 105   | MFB7      | I/O | Multi-Function Bus 7. One of twelve multi-function signals MFB[11:0].<br>Also used as HDATA1 in a 4-bit host interface configuration.                                                                                                                       |  |  |  |

| 106   | MFB6      | I/O | Multi-Function Bus 6. One of twelve multi-function signals MFB[11:0].<br>Internally pulled up. When externally pulled down (sampled at reset ) the host<br>interface is configured for 4 bits wide. In this configuration, MFB9:7 are used as<br>HDATA 3:1. |  |  |  |

| 107   | MFB5      | I/O | Multi-Function Bus 5 One of twelve multi-function signals MFB[11:0].<br>Internally pulled up. When externally pulled down (sampled at reset ) the chip<br>uses an external crystal resonator across pins 141 and 142, instead of an<br>oscillator.          |  |  |  |

| 109   | MFB4      | I/O | Multi-Function Bus 4. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                       |  |  |  |

| 110   | MFB3      | I/O | Multi-Function Bus 3. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                       |  |  |  |

| 111   | FMB2      | I/O | Multi-Function Bus 2. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                       |  |  |  |

| 112   | MFB1      | I/O | Multi-Function Bus 1. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                       |  |  |  |

| 113   | MFB0      | I/O | Multi-Function Bus 0. One of twelve multi-function signals MFB[11:0].                                                                                                                                                                                       |  |  |  |

# Table 3 : Clock Recovery / Time Base Conversion

| PIN # | Name        | I/O | Description                                                                                                                            |

|-------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 125   | DVDD        |     | Digital power for Destination DDS (direct digital synthesizer). Must be bypassed                                                       |

|       |             |     | with a 0.1uF capacitor to digital ground plane.                                                                                        |

| 127   | DAC_DGNDA   |     | Analog ground for Destination DDS DAC. Must be directly connected to the analog system ground plane.                                   |

| 100   |             |     | Analog power for Destination DDS DAC. Must be bypassed with a 0.1uF                                                                    |

| 128   | DAC_DVDDA   |     | capacitor to pin 127 (DAC_DGNDA).                                                                                                      |

| 129   | PLL_DVDDA   |     | Analog power for the Destination DDS PLL. Must be bypassed with a 0.1uF                                                                |

|       |             |     | capacitor to pin 131 (PLL_DGNDA).                                                                                                      |

| 130   | Reserved    |     | For testing purposes only. Do not connect.                                                                                             |

| 131   | PLL_DGNDA   |     | Analog ground for the Destination DDS PLL. Must be directly connected to the                                                           |

|       | _           |     | analog system ground plane.                                                                                                            |

| 132   | SUB_DGNDA   |     | Dedicated pin for the substrate guard ring that protects the Destination DDS.                                                          |

|       |             |     | Must be directly connected to the analog system ground plane.                                                                          |

| 133   | SUB_SGNDA   |     | Dedicated pin for the substrate guard ring that protects the Source DDS. Must be directly connected to the analog system ground plane. |

| 124   |             |     | Analog ground for the Source DDS PLL. Must be directly connected to the                                                                |

| 134   | PLL_SGNDA   |     | analog system ground.                                                                                                                  |

| 135   | Reserved    |     | For testing purposes only. Do not connect.                                                                                             |

| 136   | PLL_SVDDA   |     | Analog power for the Source DDS DAC. Must be bypassed with a 0.1uF                                                                     |

| 150   |             |     | capacitor to pin 134 (PLL_SGNDA)                                                                                                       |

| 137   | DAC_SVDDA   |     | Analog power for the Source DDS DAC. Must be by passed with a 0.1uF                                                                    |

|       |             |     | capacitor to pin 138 (DAC_SGNDA)                                                                                                       |

| 138   | DAC_SGNDA   |     | Analog power for the Source DDS DAC. Must be directly connected to the                                                                 |

|       |             |     | analog system ground.<br>Digital power for the Source DDS. Must be bypassed with a 0.1uF capacitor to                                  |

| 139   | SVDD        |     | digital ground plane.                                                                                                                  |

| 141   | TCLK        | Ι   | Reference clock(TCLK) input from the 50 MHz crystal oscillator                                                                         |

| 142   | XTAL        | 0   | If using an external oscillator, leave this pin floating. If using an external crystal,                                                |

|       |             |     | connect crystal between TCLK(141) and XTAL(142). See MFB5(pin 107).                                                                    |

| 143   | PLL_RVDDA   |     | Analog power for the Reference DDS PLL. Must be bypassed with a 0.1uF                                                                  |

|       |             |     | capacitor to pin 144(PLL_RGNDA)                                                                                                        |

| 144   | PLL_RGNDA   |     | Analog ground for the Reference DDS PLL. Must be directly connected to the                                                             |

|       |             |     | analog system ground plane.                                                                                                            |

| 145   | Reserved    |     | For testing purposes only. Do not connect.                                                                                             |

| 146   | SUB_RGNDA   |     | Dedicated pin for the substrate guard ring that protects the Reference DDS. Must                                                       |

|       |             |     | be directly connected to the analog system ground plane.                                                                               |

| 148   | VSYNC       | Ι   | CRT Vsync input. TTL Schmitt trigger input.                                                                                            |

| 149   | SYN_VDD     |     | Digital power for CRT Sync input.                                                                                                      |

|       |             | т   |                                                                                                                                        |

| 150   | HSYNC/CSYNC | Ι   | CRT Hsync or CRT composite sync input. TTL Schmitt trigger input.                                                                      |

# Table 4. TFT Panel Interface

| PIN #   | Name   | I/O | I/O 2mpl/ally 2mpl/ally 1mpl/ally 1mpl/ally |                   |     |                 |                   |     |  |

|---------|--------|-----|---------------------------------------------|-------------------|-----|-----------------|-------------------|-----|--|

| 1 119 # | Ivanie | 1/0 | 2pxl/clk<br>8bit                            | 2pxl/clk<br>6-bit | 1px | kl/clk<br>8-bit | 1pxl/clk<br>6-bit | TFT |  |

| 6       | PD47   | 0   | OB1                                         | _                 | -   | _               |                   |     |  |

| 7       | PD46   | 0   | OB0                                         | -                 | -   | -               |                   |     |  |

| 9       | PD45   | 0   | OG1                                         | -                 | -   | -               |                   |     |  |

| 10      | PD44   | 0   | OG0                                         | -                 | -   | -               |                   |     |  |

| 13      | PD43   | 0   | OR1                                         | -                 | -   | -               |                   |     |  |

| 14      | PD42   | 0   | OR0                                         | -                 | -   | -               |                   |     |  |

| 15      | PD41   | 0   | EB1                                         | -                 | B1  | -               |                   |     |  |

| 16      | PD40   | 0   | EB0                                         | -                 | B0  | -               |                   |     |  |

| 17      | PD39   | 0   | EG1                                         | -                 | G1  | -               |                   |     |  |

| 19      | PD38   | 0   | EG0                                         | -                 | G0  | -               |                   |     |  |

| 20      | PD37   | 0   | ER1                                         | -                 | R1  | -               |                   |     |  |

| 22      | PD36   | 0   | ER0                                         | -                 | R0  | -               |                   |     |  |

| 23      | PD35   | 0   | OB7                                         | OB5               | -   | -               |                   |     |  |

| 24      | PD34   | 0   | OB6                                         | OB4               | -   | -               |                   |     |  |

| 25      | PD33   | 0   | OB5                                         | OB3               | -   | -               |                   |     |  |

| 26      | PD32   | 0   | OB4                                         | OB2               | -   | -               |                   |     |  |

| 27      | PD31   | 0   | OB3                                         | OB1               | -   | -               |                   |     |  |

| 28      | PD30   | 0   | OB2                                         | OB0               | -   | -               |                   |     |  |

| 29      | PD29   | 0   | OG7                                         | OG5               | -   | -               |                   |     |  |

| 31      | PD28   | 0   | OG6                                         | OG4               | -   | -               |                   |     |  |

| 32      | PD27   | 0   | OG5                                         | OG3               | -   | -               |                   |     |  |

| 34      | PD26   | 0   | OG4                                         | OG2               | -   | -               |                   |     |  |

| 35      | PD25   | 0   | OG3                                         | OG1               | -   | -               |                   |     |  |

| 36      | PD24   | 0   | OG2                                         | OG0               | -   | -               |                   |     |  |

| 37      | PD23   | 0   | OR7                                         | OR5               | -   | -               |                   |     |  |

| 38      | PD22   | 0   | OR6                                         | OR4               | -   | -               |                   |     |  |

| 39      | PD21   | 0   | OR5                                         | OR3               | -   | -               |                   |     |  |

| 42      | PD20   | 0   | OR4                                         | OR2               | -   | -               |                   |     |  |

| 46      | PD19   | Ο   | OR3                                         | OR1               | -   | -               |                   |     |  |

| 47      | PD18   | Ο   | OR2                                         | OR0               | -   | -               |                   |     |  |

| 48      | PD17   | 0   | EB7                                         | EB5               | B7  | B5              |                   |     |  |

| 50      | PD16   | 0   | EB6                                         | EB4               | B6  | B4              |                   |     |  |

| 51      | PD15   | 0   | EB5                                         | EB3               | B5  | B3              |                   |     |  |

| 52      | PD14   | 0   | EB4                                         | EB2               | B4  | B2              |                   |     |  |

| 53      | PD13   | 0   | EB3                                         | EB1               | B3  | B1              |                   |     |  |

| 54      | PD12   | 0   | EB2                                         | EB0               | B2  | B0              |                   |     |  |

| 55      | PD11   | 0   | EG7                                         | EG5               | G7  | G5              |                   |     |  |

| 56      | PD10   | 0   | EG6                                         | EG4               | G6  | G4              |                   |     |  |

| 57      | PD9    | 0   | EG5                                         | EG3               | G5  | G3              |                   |     |  |

| 62      | PD8    | 0   | EG4                                         | EG2               | G4  | G2              |                   |     |  |

| PIN # | Name   | I/O | 2pxl/clk<br>8bit                                                               | 2pxl/clk<br>6-bit                            | 1pxl      | Descript<br>/clk<br>S-bit | tion<br>1pxl/clk<br>6-bit | TFT                       |

|-------|--------|-----|--------------------------------------------------------------------------------|----------------------------------------------|-----------|---------------------------|---------------------------|---------------------------|

| 63    | PD7    | 0   | EG3                                                                            | EG1                                          | G3        | G1                        |                           |                           |

| 64    | PD6    | 0   | EG2                                                                            | EG0                                          | G2        | G0                        |                           |                           |

| 66    | PD5    | 0   | ER7                                                                            | EG5                                          | R7        | R5                        |                           |                           |

| 67    | PD4    | 0   | ER6                                                                            | ER4                                          | R6        | R4                        |                           |                           |

| 68    | PD3    | 0   | ER5                                                                            | ER3                                          | R5        | R3                        |                           |                           |

| 69    | PD2    | 0   | ER4                                                                            | ER2                                          | R4        | R2                        |                           |                           |

| 70    | PD1    | 0   | ER3                                                                            | ER1                                          | R3        | R1                        |                           |                           |

| 71    | PD0    | 0   | EG2                                                                            | ER0                                          | R2        | R0                        |                           |                           |

| 43    | PdispE | 0   | This output pr                                                                 | ovides a par                                 | el displ  | ay enabl                  | e signal that             | is active when flat panel |

|       |        |     | data is valid.                                                                 |                                              |           |                           |                           |                           |

| 74    | PHS    | 0   | This output pr                                                                 | ovides the p                                 | anel line | e clock s                 | signal.                   |                           |

| 73    | PVS    | 0   | This output pr                                                                 | This output provides the frame start signal. |           |                           |                           |                           |

| 44    | PCLKA  | 0   | This output is used to drive the flat panel shift clock.                       |                                              |           |                           |                           |                           |

| 45    | PCLKB  | 0   | Same as PCLKA above.                                                           |                                              |           |                           |                           |                           |

|       |        |     | The polarity as                                                                | nd the phase                                 | of this   | signal a                  | re independe              | ntly programmable.        |

| 75    | Pbias  | 0   | This output is used to turn on/off the panel bias power or controls backlight. |                                              |           |                           |                           |                           |

| 76    | Ppwr   | 0   | This output is                                                                 | used to cont                                 | rol the p | power to                  | a flat panel.             |                           |

# Table 5. Test Pins

| PIN # | Name      | I/O | Description                                                                                                             |

|-------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 3     | PSCAN     | Ι   | Enable automatic PCB assembly test. When this input is pulled high, the                                                 |

|       |           |     | automatic PCB assembly test mode is entered. An internal pull-down resistor drives this input low for normal operation. |

| 155   | SCAN_IN1  | Ι   | Scan input 1 used for automatic PCB assembly tesing.                                                                    |

| 157   | SCAN_IN2  | Ι   | Scan input 2 used for automatic PCB assembly tesing.                                                                    |

| 159   | SCAN_OUT1 | 0   | Scan output 1 used for automatic PCB assembly tesing.                                                                   |

| 160   | SCAN_OUT2 | 0   | Scan output 2 used for automatic PCB assembly tesing.                                                                   |

| 153   | Reserved  |     |                                                                                                                         |

| 154   | Reserved  |     |                                                                                                                         |

# Table 6. VDD / VSS for Core Circuitry, Host Interface, and Panel/Memory Interface

| PIN #                            | Description                                                     |

|----------------------------------|-----------------------------------------------------------------|

| 65, 40, 33, 12                   | PVDD4~PVDD1 for panel / memory interface. Connect to +3.3V.     |

|                                  | Must be the same voltage as the CVDD's                          |

| 149, 108, 58, 21, 11             | SRVDD2-1, CVDD4, CVDD2-1 for core circuitry. Connect to +3.3V.  |

| 119, 100, 50, 21, 11             | Must be the same voltage as the PVDD's.                         |

| 158, 151, 140, 126, 114, 72, 61, | Disital arounds for some simplim, and manal (mamony interface   |

| 49, 41, 30, 18, 8, 1             | Digital grounds for core circuiry and panel / memory interface. |

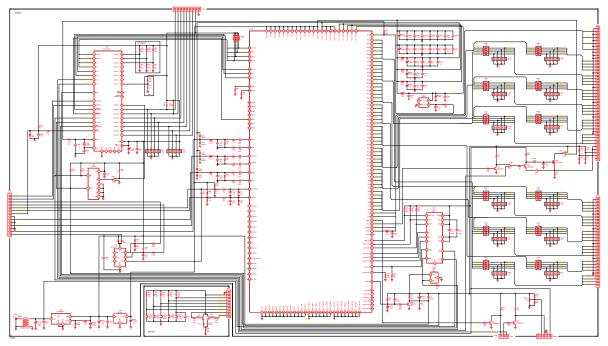

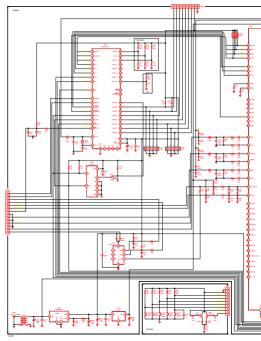

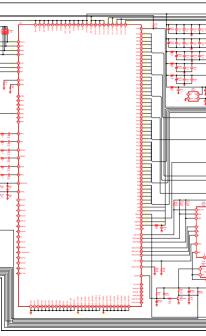

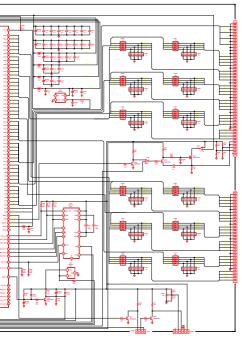

### 1.4 System-level Block Diagram

Figure 2. Typical Stand-alone Configuration

#### **1.5 Operating Modes**

The Source Clock (also called SCLK in this document) and the Panel Clock are defined as follows:

- The Source Clock is the sample clock regenerated from the input Hsync timing (called clock recovery) by SCLK DDS (direct digital synthesis) and the PLL.

- The Panel Clock is the timing clock for panel data at the single pixel per clock rate. The actual PCLK to the panel may be one-half of this frequency for double-pixel panel data format. When its frequency is different from that of source clock, the panel clock is generated by Destination Clock (or DCLK) DDS/PLL.

There are six display modes: Native, Slow DCLK, Zoom, Downscaling, Destination Stand Alone, and Source Stand Alone.

Each mode is unique in terms of:

- S Input video resolution vs. panel resolution

- Source Clock frequency / Panel Clock frequency ratio

- Source Hsync frequency / Panel Hsync frequenc ratio

- Z Data source (analog RGB, panel background color, on-chip pattern generator

#### 1.5.1 Native

Panel Clock frequency = Source Clock frequency Panel Hsync frequency = Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution and the input data clock frequency is within the panel clock frequency specification of the panel being used.

#### 1.5.2 Slow DCLK

Panel Clock frequency < Source Clock frequency Panel Hsync frequency = Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution, but the input data clock frequency is exceeds the panel clock frequency specification of the panel being used. The panel clock is scaled to the Source Clock, and the internal data buffers are used to spread out the timing of the input data by making use of the large CRT blanking time to extends the panel horizontal display time.

#### 1.5.3 Zoom

Panel Clock frequency > Source Clock frequency Panel Hsync frequency > Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is less than the panel resolution. The input data clock is then locked to the pnael clock, which is at a higher frequency. The input data is zoomed to the panel resolution.

#### 1.5.4 Downscaling

Panel Clock frequency < Source Clock frequency Panel Hsync frequency < Input Hsync frequency Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is greater than the panel resolution, to provide enough of a display to enable the user to recover to a supported resolution. The input clock is operated at a frequency less than that of the input pixel rate(under-sampled horizontally) and the scaling filter is used to drop input lines. In this mode, zoom scaling must be disabled

#### 1.5.5 Destination Stand Alone

Panel Clock = DCLK in open loop (not locked) Panel Hsync frequency = DCLK frequency / (Destination Htotal register value) Panel Vsync frequency = DCLK frequency / (Dest. Htotal register value \* Dest. Vtotal register value)

This mode is used when the input is changing or not available. The OSD may still be used as in all other display modes and stable panel timing signals are produced. This mode may be automatically set when the gmZAN1 detects input timing changes that could cause out- of-spec operation of the panel.

#### 1.5.6 Source Stand Alone

Panel Clock = DCLK in open loop (not locked to input Hsync) Panel Hsync frequency = SCLK frequency / (Source Htotal register value) Panel Vsync frequency = SCLK frequency / (Source Htotal register value \*Source Vtotal register value)

This mode is used to display the pattern generator data. This mode may be useful for testing an LCD panel on the manufacturing line (color temperature calibration, etc.).

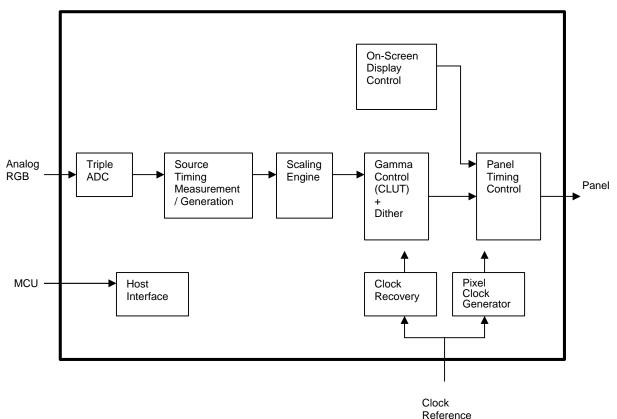

#### 2. FUNCTIONAL DESCRIPTION

Figure 3 below shows the main functional blocks inside the gmZAN1

# 2.1 Overall Architecture

Figure 3. Block Diagram for gmZAN1

# 2.2 Clock Recovery Circuit

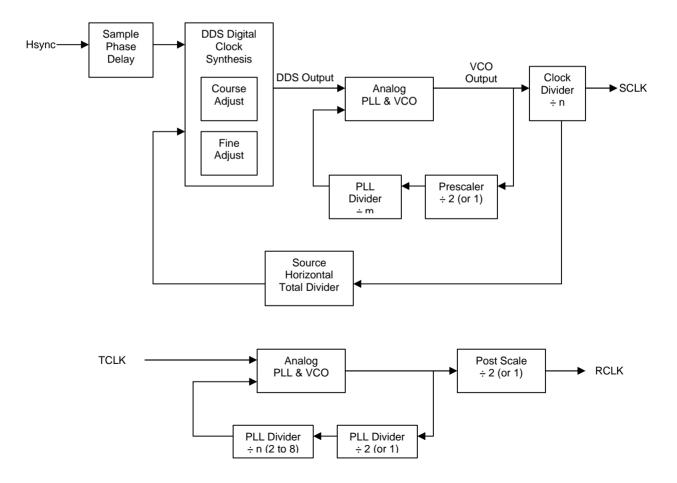

The gmZAN1 has a built-in clock recovery circuit. This circuit consists of a digital clock synthesizer and an analog PLL. The clock recovery circuit generates the clock used to sample analog RGB data (SCLK or source clock). This circuit is locked to the HSUNC of the incoming video signal. The RCLK generated from the TCLK input is used as a reference clock.

The clock recovery circuit adjusts the SCLK period so that the feedback pulse generated every SCLK period multiplied by the Source Horizontal Total value (as programmed into the registers) locks to the rising edge of the Hsync input. Even though the initial SCLK frequency and the final SCLK frequency are as far apart as 60MHz, locking can be achieved in less than 1ms across the operation voltage/temperature range.

The SCLK frequency (1/SCLK period) can be set to the range of 10-to-135 MHz. Using the DDS (direct digital synthesis) technology the clock recovery circuit can generate any SCLK clock frequency within this range.

The pixel clock (DCLK or destination clock) is used to drive a panel when the panel clock is different from SCLK (or SCLK/2). It is generated by a circuit virtually identical to the clock recovery circuit. The difference is that DCLK is locked to SCLK while SCLK is locked to the Hsync input. DCLK frequency divided by N is locked to SCLK frequency divided by M. The value M and N are calculated and programmed in the register by firmware. The value M should be close to the Source Htotal value.

The table below summarizes the characteristics of the clock recovery circuit.

#### **Table 7. Clock Recovery Characteristics**

|                           | Minimum | Typical               | Maximum |

|---------------------------|---------|-----------------------|---------|

| SCLK Frequency            | 10MHz   |                       | 135 MHz |

| Sampling Phase Adjustment |         | 0.5 ns/step, 64 steps |         |

Patented digital clock synthesis technology makes the gmZAN1 clock circuits very immune to temperature/voltage drift.

### 2.2.1 Sampling Phase Adjustment

The ADC sampling phase is adjusted by delaying the Hsync input at the programmable delay cell inside the gmZAN1. The delay value can be adjusted in 64 steps, 0.5 ns/step. The accuracy of the sampling phase is checked by the gmZAN1 and the "score" can be read in a register. This feature will enable accurate auto-adjustment of the ADC sampling phase.

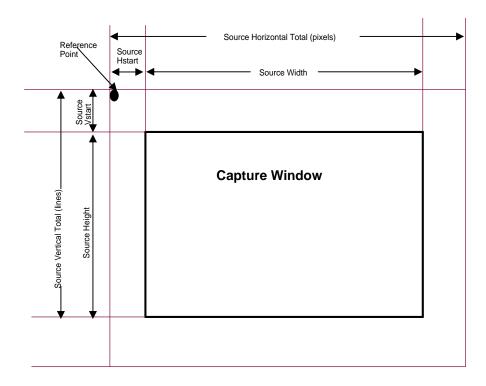

### 2.2.2 Source Timing Generator

The STG module defines a capture window and sends the input data to the data path block. The figure below shows how the window is defined.

For the horizontal direction, it is defined in SCLKs (equivalent to a pixel count). For the vertical direction, it is defined in lines.

All the parameters in the figure that begin with "Source" are programmed into the gmZAN1 registers.

Note that the vertical total is solely determined by the input.

The reference point is as follows:

- The first pixel of a line: the pixel whose SCLK rising edge sees the transition of the HSYNC polarity from low to high.

- The first line of a frame: the line whose HSYNC rising edge sees the transition of the VSYNC polarity from low to high.

The gmZAN1 also supports the use of analog composite sync and digital sync signals as described in Section 2.3.2

#### Figure 5. Capture Window

#### 2.3 Analog-to-Digital Converter

#### **2.3.1 Pin Connection**

The RGB signals are to be connected to the gmZAN1 chip as described in Table 8 and Table 9.

| GmZAN1 Pin Name (Pin Number) | CRT Signal Name                                |

|------------------------------|------------------------------------------------|

| Red+(#95)                    | Red                                            |

| Red- (#94)                   | N/A (Tie to Analog GND for Red on the board)   |

| Green+(#91)                  | Green                                          |

| Green- (#90)                 | N/A (Tie to Analog GND for Green on the board) |

| Blue+(#87)                   | Blue                                           |

| Blue- (#86)                  | N/A (Tie to Analog GND for Blue on the board)  |

| HSYNC/CS (#150)              | Horizontal Sync                                |

| VSYNC (#148)                 | Vertical Sync                                  |

Table 8. Pin Connection for RGB Input with Hsync/Vsync

#### Table 9. Pin Connection for RGB Input with Composite Sync

| GmZAN1 Pin Name (Pin Number) | CRT Signal Name                                                   |

|------------------------------|-------------------------------------------------------------------|

| Red+(#95)                    | Red                                                               |

| Red- (#94)                   | N/A (Tie to Analog GND for Red on the board)                      |

| Green+(#91)                  | Green                                                             |

|                              | When using Sync-On-Green this signal also carries the sync pulse. |

| Green- (#90)                 | N/A (Tie to Analog GND for Green on the board)                    |

| Blue+(#87)                   | Blue                                                              |

| Blue- (#86)                  | N/A (Tie to Analog GND for Blue on the board)                     |

| HSYNC/CS (#150)              | Digital composite sync. Not applicable for Sync-On-Green          |

The gmZAN1 chip has three ADC's (analog-to-digital converters), one for each color (red, green, and blue). Table 10 summarizes the characteristics of the ADC.

#### **Table 10. ADC Characteristics**

| MIN                         | ТҮР            | MAX                                                                                                                                                                 | NOTE                                                                                                                                                                                  |  |  |  |  |

|-----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RGB Track & Hold Amplifiers |                |                                                                                                                                                                     |                                                                                                                                                                                       |  |  |  |  |

|                             | 160MHz         |                                                                                                                                                                     |                                                                                                                                                                                       |  |  |  |  |

|                             | 8.5ns          |                                                                                                                                                                     | Full Scale Input = 0.75V, BW=160MHz(*)                                                                                                                                                |  |  |  |  |

| 0.45V                       |                | 0.95V                                                                                                                                                               |                                                                                                                                                                                       |  |  |  |  |

|                             | +/-1 LSB       |                                                                                                                                                                     | Measured @ ADC Output (**)                                                                                                                                                            |  |  |  |  |

|                             |                |                                                                                                                                                                     | For a larger DC offset from an external video source, the AC coupling feature is used to remove the offset.                                                                           |  |  |  |  |

|                             | +/-1 LSB       |                                                                                                                                                                     | Measured @ ADC Output                                                                                                                                                                 |  |  |  |  |

|                             |                |                                                                                                                                                                     |                                                                                                                                                                                       |  |  |  |  |

| 20MHz                       |                | 110MHz                                                                                                                                                              |                                                                                                                                                                                       |  |  |  |  |

|                             |                | +/- 0.9LSB                                                                                                                                                          | fs = 80 MHz                                                                                                                                                                           |  |  |  |  |

|                             | +/- 1.5LSB     |                                                                                                                                                                     | fs = 80 MHz                                                                                                                                                                           |  |  |  |  |

|                             | +/- 0.5LSB     |                                                                                                                                                                     |                                                                                                                                                                                       |  |  |  |  |

|                             | 7 Bits         |                                                                                                                                                                     | fin = 1MHz, fs=80 MHz Vin= -1db below<br>full scale=0.75V                                                                                                                             |  |  |  |  |

|                             | 400mW          |                                                                                                                                                                     | fs=110 MHz, Vdd=3.3V                                                                                                                                                                  |  |  |  |  |

|                             |                | 100uA                                                                                                                                                               |                                                                                                                                                                                       |  |  |  |  |

|                             | 0.45V<br>20MHz | 160MHz         8.5ns         0.45V         +/-1 LSB         +/-1 LSB         20MHz         20MHz         +/- 1.5LSB         +/- 0.5LSB         7 Bits         400mW | 160MHz         8.5ns         0.45V         +/-1 LSB         +/-1 LSB         +/-1 LSB         20MHz         +/-1 LSB         20MHz         +/-1 LSB         +/-1 LSB         +/-1 LSB |  |  |  |  |

(\*) Guaranteed by design (\*\*) Independent of full scale R,G,B input

The gmZAN1 ADC has a built-in clamp circuit. By inserting series capacitors (about 10 nF) the DC offset of an external video source can be removed. The clamp pulse position and width are programmable.

#### 2.3.2 Sync. Signal Support

The gmZAN1 chip supports digital separate sync (Hsync/Vsync), digital composite sync, and analog composite sync (also known as sync-on-green). All sync types are supported without external sync separation / extraction circuits.

#### **Digital Composite Sync**

The types of digital composite sync inputs supported are:

- Solution CR/AND type: No Csync pulses toggling during the vertical sync period

- XOR type: Csync polarity changes during the vertical sync period

The gmZan1 provides enough sync status information for the firmware to detect the digital composite sync type.

#### Sync-On-Green (Analog Composite Sync)

The voltage level of the sync tip during the vertical sync period can be either -0.3V or 0V

#### 2.3.3 Display Mode Support

A mode calculation utility (MODECALC.EXE) provided by Genesis Microchip may be run before compilation of the firmware to determine which input modes can be supported. Refer to firmware documents for more details.

#### 2.4 Input Timing Measurement

As described in section 2.2.2 above, input data is sent from the analog-to-digital converter to the source timing generator (STG) block. The STG block defines a capture window (Figure 5).

The input timing measurement block consists of the source timing measurement (STM) block and interrupt request (IRQ) controller. Input timing parameters are measured by the STM block and stored in registers. Some input conditions will generate an IRQ to an external micro-controller. The IRQ generating conditions are programmable.

#### 2.4.1 Source Timing Measurement

When it receives the active CRT signal (R,G,B and Sync signals) the Source Timing Measurement unit begins measuring the horizontal and vertical timing of the incoming signal using the sync signals and TCLKi as a reference. Horizontal measurement occurs by measuring a minimum and a maximum value for each parameter to account for TCLKi sampling granularity. The measured value is updated every line. Vertical parameters are measured in terms of horizontal lines. The trailing edge of the Hsync input is used to check the polarity of the Vsync input. The table below lists all the parameters that may be read in the source timing measurement (STM) registers of the gmZAN1.

| Table 11. Input Timing Parameters Measured by the STM Block |                   |                                                       |  |  |  |  |

|-------------------------------------------------------------|-------------------|-------------------------------------------------------|--|--|--|--|

| Parameter                                                   | Unit              | Updated at:                                           |  |  |  |  |

| HSYNC Missing                                               | N/A               | Every 4096 TCLKs and every 80ms (2-bits)              |  |  |  |  |

| VSYNC Missing                                               | N/A               | Every 80ms                                            |  |  |  |  |

| HSYNC/VSYNC Timing Change                                   | N/A               | When the horizontal period delta or the vertical      |  |  |  |  |

|                                                             |                   | period delta to the previous line / frame exceeds the |  |  |  |  |

|                                                             |                   | threshold value (programmable).                       |  |  |  |  |

| HSYNC Polarity                                              | Positive/Negative | After register read                                   |  |  |  |  |

| VSYNC Polarity                                              | Positive/Negative | Every frame                                           |  |  |  |  |

| Horizontal Period Min/Max                                   | TCLKs and SCLKs   | After register read                                   |  |  |  |  |

| HSYNC High Period Min/Max                                   | TCLKs             | After register read                                   |  |  |  |  |

| Vertical Period                                             | Lines             | Every frame                                           |  |  |  |  |

| VSYNC High Period                                           | Lines             | Every frame                                           |  |  |  |  |

| Horizontal Display Start                                    | SCLKs             | Every frame                                           |  |  |  |  |

| Horizontal Display End                                      | SCLKs             | Every frame                                           |  |  |  |  |

| Vertical Display Start                                      | Lines             | Every frame                                           |  |  |  |  |

| Vertical Display End                                        | Lines             | Every frame                                           |  |  |  |  |

| Interlaced Input Detect                                     | N/A               | Every frame                                           |  |  |  |  |

| CRC Data/Line Data                                          | N/A               | Every frame                                           |  |  |  |  |

| CSYNC Detect                                                | N/A               | Every 80ms                                            |  |  |  |  |

Table 11. Input Timing Parameters Measured by the STM Block

The display start/end registers store the first and the last pixels/lines of the last frame that have RGB data above a programmed threshold.

The reference point of the STM block is the same as that of the source timing generator (STG) block:

The first pixel: the pixel whose SCLK rising edge sees the transition of the HSYNC polarity from low to high.

The first line: the line whose HSYNC rising edge sees the transition of the VSYNC polarity from low to high.

#### The CRC data and the line data are used to detect a test pattern image sent to the gmZAN1 input port.

### 2.4.2 IRQ Controller

Some input timing conditions can cause the gmZAN1 chip to generate an IRQ. The IRQ-generating conditions are programmable, as given in the following table.

| Table 12. IRQ-Generation Conditions |                                                      |  |  |  |  |

|-------------------------------------|------------------------------------------------------|--|--|--|--|

| IRQ Event                           | Remark                                               |  |  |  |  |

| Timing Event                        | One of the three events:                             |  |  |  |  |

|                                     | <ul> <li>Leading edge of Vsync input,</li> </ul>     |  |  |  |  |

|                                     | A Panel line count (the line count is programmable), |  |  |  |  |

|                                     | ∠ Every 10ms                                         |  |  |  |  |

|                                     | Only one event may be selected at a time.            |  |  |  |  |

| Timing Change                       | Any of the following timing changes:                 |  |  |  |  |

|                                     | ∠ Sync loss,                                         |  |  |  |  |

|                                     | ∠ DDS tracking error beyond threshold,               |  |  |  |  |

|                                     | Morizontal/vertical timing change beyond threshold   |  |  |  |  |

|                                     | Threshold values are programmable.                   |  |  |  |  |

Reading the IRQ status flags will not affect the STM registers.

Note that if a new IRQ event occurs while the IRQ status register is being read, the IRQ signal will become inactive for minimum of one TCLK period and then get re-activated. The polarity of the IRQ signal is programmable.

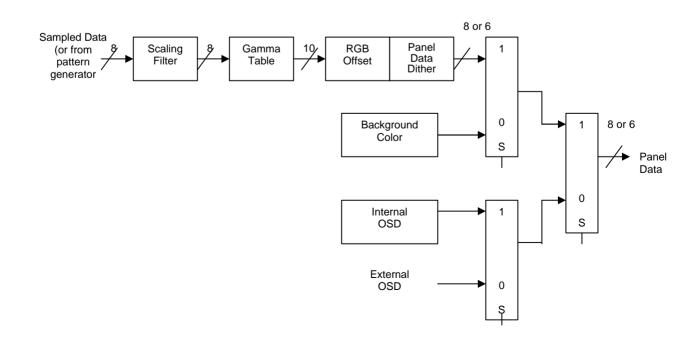

#### 2.5 Data Path

The data path block of gmZAN1 is shown in Figure 6.

#### Figure 6. gmZAN1 Data Path

#### 2.5.1 Scaling Filter

The gmZAN1 scaling filter uses an advanced adaptive scaling technique proprietary to Genesis Microchip Inc. and provides high quality scaling of real time video and graphics images. This is Genesis' third generation scaling technology that benefits from the expertise and feedback gained by supporting a wide range of solutions and applications.

#### 2.5.2 Gamma Table

The gamma table is used to adjust the RGB data for the individual display characteristics of the TFT panel. The overall gamma of the display may be set, as well as separate corrections for each of the three display channels. In addition, the gamma table may be used for contrast, brightness, and white balance (temperature) adjustments. The lookup table has an 8-bit input (256 different RGB entries) and produces a 10-bit output.

#### 2.5.3 RGB Offset

The RGB offsets provide a simple shift (positive or negative) for each of the three color channels. This may be used as a simple brightness adjustment within a limited range. The data is clamped to zero for negative offsets, and clamped to FFh for positive offsets. This adjustment is much faster than recalculating the gamma table, and could be used with the OSD user controller to provide a quick brightness adjust. An offset range of plus 127\*4 to minus 127\*4 is available.

#### 2.5.4 Panel Data Dither

For TFT panels that have fewer than eight bits for each R,G,B input, the gmZAN1 provides ordered and random dithering patterns to help smoothly shade colors on 6-bit panels.

#### 2.5.5 Panel Background Color

A solid background color may be selected for a border around the active display area. The background color is most often set to black.

#### **2.6 Panel Interface**

The gmZAN1 chip interfaces directly with all of today's commonly used active matrix flat panels with 640x480, 800x600 and 1024x768 resolutions. The resolution and the aspect ratio are NOT limited to specific values.

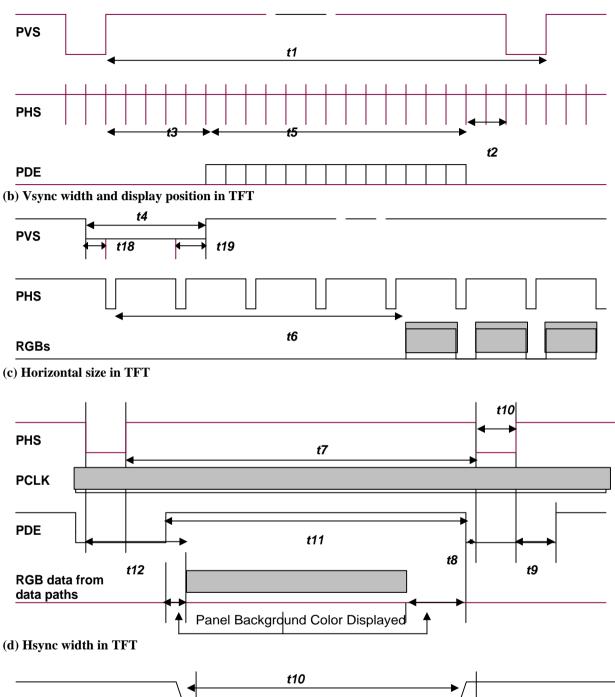

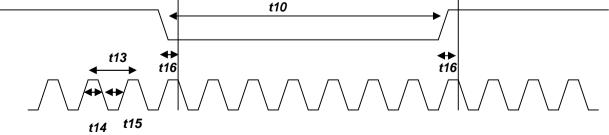

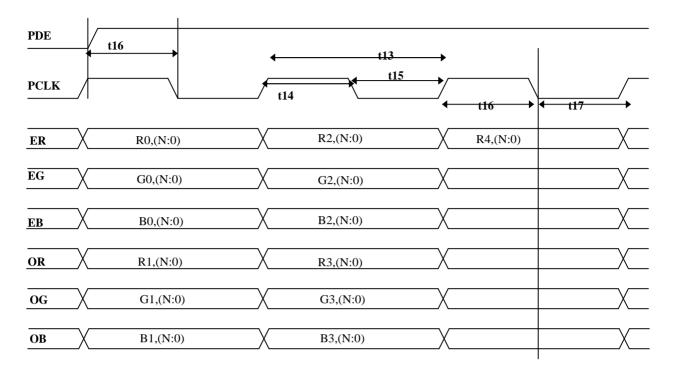

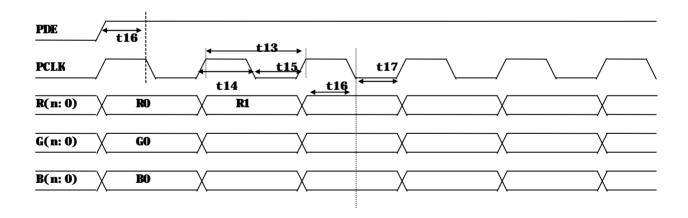

#### 2.6.1 TFT Panel Interface Timing Specification

The TFT panel interface timing parameters are listed in Table 13 below. Refer to three timing diagrams of Figure 7 and Figure 8 for the timing parameter definition. All aspects of the gmZAN1 interface are programmable. For horizontal parameters, Horizontal Display Enable Start, Horizontal Display Enable End, Horizontal Sync Start and Horizontal Sync End are programmable. Vertical Display Enable Start, Vertical Display Enable End, Vertical Sync Start and Vertical Sync End are also fully programmable.

In order to maximize panel data setup and hold time, the panel clock (PCLKA, PCLKB) output skew is programmable. In addition, the current drive strength of the panel interface pins is programmable.

| Signal Nam | e                   |     | Min               | Typical           | Max               | Unit       |

|------------|---------------------|-----|-------------------|-------------------|-------------------|------------|

| PVS        | Period              | t1  | 0                 | 16.67             | 2048              | lines      |

|            |                     |     |                   |                   | -                 | ms         |

|            | Frequency           |     |                   | 60                | -                 | Hz         |

|            | Front porch         | t2  | 0                 |                   | 2048              | lines      |

|            | Back porch          | t3  | 0                 |                   | 2048              | lines      |

|            | Pulse width         | t4  | 0                 |                   | 2048              | lines      |

|            | PdispE              | t5  | 0                 | Panel height      | 2048              | lines      |

|            | Disp. Start from VS | t6  | 0                 |                   | 2048              | lines      |

|            | PVS set up tp PHS   | t18 | 1                 |                   | 2048              | PCLK *1    |

|            | PVS hold from PHS   | t19 | 1                 |                   | 2048              | PCLK *1    |

| PHS        | Period              | t7  | 0                 |                   | 2048 [1024        | PCLK *1    |

|            | Front porch         | t8  | 0                 |                   | 2048              | PCLK *1    |

|            | Back porch          | t9  | 0                 |                   | 2048              | PCLK *1    |

|            | Pulse width         | t10 | 0                 |                   | 2048              | PCLK *1    |

|            | PdispE              | t11 | 0                 | Panel width       | 2048 [1024]       | PCLK *1    |

|            | Disp. Start fom HS  | t12 | 0                 |                   | 2048              | PCLK *1    |

| PCLKA,     | Frequency           | t13 |                   |                   | 120 [60]          | MHz        |

| PCLKB*4    | Clock (H) *2        | t14 | DCLK/2-3 [DCLK-3] |                   | DCLK/2-2 [DCLK-2] | ns         |

|            | Clock (L) *2        | t15 | DCLK/2-3 [DCLK-3] |                   | DCLK/2-2 [DCLK-2] | ns         |

|            | Туре                |     | -                 | One pxl/clock     | -                 |            |

|            |                     |     |                   | [two pxl/clock]   |                   |            |

| Data       | Set up *3           | t16 | DCLK/2-5 [DCLK-5] |                   | DCLK/2-2 [DCLK-2] | ns         |

|            | Hold *3             | t17 | DCLK/2-5 [DCLK-5] |                   | DCLK/2-2 [DCLK-2] | ns         |

|            | width               |     | 3 bits            | 18 bits [36 bits] | 24 bits [48 bits] | bits/pixel |

#### Table 13. gmZAN1 TFT Panel Interface Timing

**NOTE:** Numbers in [] are for two pixels/clock mode.

**NOTE:** The drive current of the panel interface signals is programmable as shown in Table 1. The drive current is to be programmed through the API upon chip initialization. Output current is programmable from 2 mA to 20mA in increments of 2 mA. Drive strength should be programmed to match the load presented by the cable and input of the panel. Values shown are based on a loading of 20pF and a drive strength of 8 mA.

NOTE \*1: The PCLK is the panel shift clock.

NOTE \*2: The DCLK stands for Destination Clock (DCLK) period. Is equal to:

-PCLK period in one pixel/clock mode,

-twice the PCLK period in two pixels/clock mode.

- **NOTE** \*3: The setup/hold time spec. for PCLK also applies to PHS and PdispE. The setup time (t16) and the hold time (t17) listed in this table are for the case in which no clock-to-data skew is added. The PVS/PHS/PdispE/Pdata signals are asserted on the rising edge of the PCLK. The polarity of the PCLK and its skew are programmable. Clock to Data skew can be adjusted in sixteen 800-ps increments. In combination with the PCLK polarity inversion, the clock-to-data phase can be adjusted in total of 31 steps.

- NOTE \*4: The polarity of the PCLKA and the PCLKB are independently programmable.

The microcontroller must have all the timing parameters of the panel used for the monitor. The parameters are to be stored in a non-volatile memory. As can be seen from this table, the wide range of timing programmability of the gmZAN1 panel interface makes it possible to support various kinds of panels known today:

Figure 7. timing Diagrams of the TFT Panel Interface (One pixel per clock)

#### Figure 8. Data latch timing of the TFT Panel Interface

#### (a) Two pixel per clock mode in TFT

#### (b) One pixel per clock mode in TFT

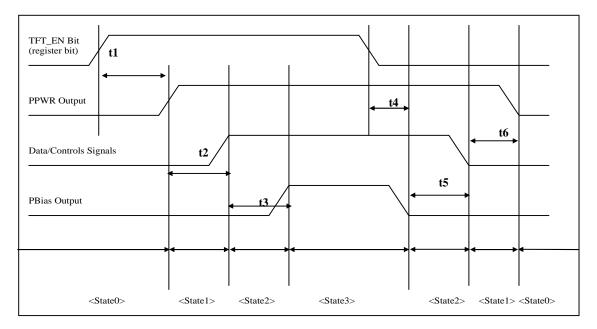

#### 2.6.2 Power Manager